Fabricação de dispositivos semicondutores

Aspeto

(Redirecionado de 32 nanômetros)

| Fabricação de dispositivos semicondutores |

Fabricação de dispositivos semicondutores é o processo utilizado para criar os circuitos integrados que estão presentes em todos os dispositivos eletrônicos. É uma sequência de passos múltiplos com litografia e utilização de produtos químicos durante a qual os circuitos eletrônicos são criados gradualmente em uma wafer feita de material semicondutor. Silício é quase sempre utilizado, mas vários compostos semicondutores são utilizados para aplicações especializadas.[1]

Lista de semicondutores

[editar | editar código-fonte]

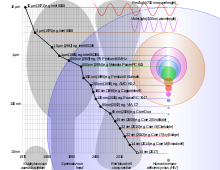

- A fabricação de dispositivos semicondutores de 7 nanômetros (7 nm) é a tecnologia seguida a de 10 nm.[2] Em 2002, a IBM produz transistor em 6nm.[3] Em 2003, a NEC produz transistor em 5 nm.[4] Em 2012, a IBM produz transistor menores que 10 nm com nanotubos de carbono.[5] Em abril de 2015 a TSMC anuncia que vai produzir transistor de 7 nm em 2017.[6] Em julho do mesmo ano a IBM anuncia chips de 7 nanômetros funcionais, usando silício-germânio.[7] Em maio de 2019 a AMD anuncia a nova linha de processadores Ryzen 3000 com o processo em 7nm.[7]

- A fabricação de semicondutores de 10 nanômetros (10 nm) é a tecnologia seguida a de 14 nm. A nomeação original deste nó "11 nm" vem da International Technology Roadmap para Semiconductors.[8] Embora o roteiro tenha sido baseado na expansão continuada das CMOS, este roteiro não garante que as CMOS baseada em silício vão conseguir ir tão longe. Isto por que o comprimento da porta dielétrica para esse nó pode ser menor do que 6 nm de espessura isto exige uma monocamada ainda menor. Estimativas indicam que os transistores nestas dimensões são significativamente afetados por tunelamento quântico. Como resultado, a evolução não-silício da CMOS, utilizando materiais ultra-low-k ou nanotubos /nanofios , bem como plataformas não-CMOS, incluindo a eletrônica molecular e dispositivos de elétrons únicos , foram propostos. Assim, este nó marca o início prático da nanoeletrônica.

- A fabricação de semicondutores de 14 nanômetros (14 nm) é a tecnologia seguida a de 22 nm / (20 nm). A nomeação desta tecnologia como "14 nm" veio da International Technology Roadmap para Semiconductors. A tecnologia de 14 nm foi alcançada em dispositivos por empresas de semicondutores em 2014.[9] A resolução de 14 nm é difícil de conseguir em um polímero, mesmo com a litografia por feixe de elétrons. Além disso, os efeitos químicos da radiação ionizante também limitar resoluções fiáveis a cerca de 30 nm, o que é também possível utilizando a tecnologia de litografia de imersão.

- A fabricação de semicondutores de 22 nanômetros (22 nm) é a tecnologia seguida a de 32 nm. A tecnologia de 22 nm foi alcançada em dispositivos por empresas de semicondutores em 2012.[10]

- A fabricação de semicondutores de 32 nanômetros (32 nm) é a tecnologia seguida a de 45 nm. A tecnologia de 32 nm foi alcançada em dispositivos por empresas de semicondutores em 2010.[11] Intel e AMD começaram a comercializar juntas microchips produzidos utilizando o processo de 32 nanômetros em 2010. IBM também desenvolveu dispositivos de 32 nm com high-k metal gate.

- A fabricação de semicondutores de 45 nanômetros (45 nm) é a tecnologia seguida a de 65 nm. A tecnologia de 45 nm foi alcançada em dispositivos por empresas de semicondutores em 2007.[12]

Ver também

[editar | editar código-fonte]Referências

- ↑ IEEE. Disponível em <http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=6570490>. Acesso em 24 de maio de 2015. (em inglês)

- ↑ 7 nm. Disponível em <http://www.eetimes.com/document.asp?doc_id=1323865>. Acesso em 09 de julho de 2015. (em inglês)

- ↑ IBM menor transistor de silício do mundoAcesso em 09 de julho de 2015.(em inglês)

- ↑ NEC menor transistor do mundo..Acesso em 09 de julho de 2015.(em inglês)

- ↑ «IBM: transistor com nanotubos de carbono»Acesso em 09 de julho de 2015.(em inglês)

- ↑ TSMC 10 nm em 2016 e 7 nm em 2017Acesso em 09 de julho de 2015.(em inglês)

- ↑ «IBM anuncia chips de 7 nanômetros; entenda como isso é revolucionário». www.tecmundo.com.br. Consultado em 19 de março de 2023

- ↑ 10 nm. Disponível em <http://www.extremetech.com/tag/10nm>. Acesso em 09 de julho de 2015. (em inglês)

- ↑ «Intel Technology Innovations and Breakthroughs». Intel (em inglês). Consultado em 19 de março de 2023

- ↑ «Intel Technology Innovations and Breakthroughs». Intel (em inglês). Consultado em 19 de março de 2023

- ↑ «Empresa Intel | Soluções para data center, Internet das coisas e...». Intel. Consultado em 19 de março de 2023

- ↑ «Acelere seu crescimento com Intel® Partner Alliance». Intel. Consultado em 19 de março de 2023

Ligações externas

[editar | editar código-fonte]- «Site com informações sobre semicondutores» (em inglês)

Fotolitografia em Dispositivos Semicondutores:

[editar | editar código-fonte]- Preparação do Substrato:

* O substrato, geralmente feito silício (Si) monocristalino, Fosfeto de indio (InP), Germanio (Ge) e Arseneto de Gálio (GaAs) , passa por um processo meticuloso de purificação para remover impurezas. O substrato é polido para garantir uma superfície lisa e uniforme, essencial para a criação precisa do circuito. Quando trabalhamos com o substrato fracionado, ou seja, não utilizamos por completo assim que retirado da embalagem é necessário realizar um procedimento de limpeza da superfície antes de iniciar o processo de fotolitografia. São utilizados os solventes Tricloretileno (TCE), acetona (100 %) e o Isopropanol (IPA) na respectiva ordem por um período de 5 minutos entre cada solução. Feito isso, é realizado a secagem com o gás de nitrogênio.

- Revestimento da Camada Fotossensível:

* A camada de resist é aplicada por meio de técnicas como spin coating, onde o substrato gira rapidamente, distribuindo uniformemente o resist. Este resist é uma substância polimérica sensível à luz, podendo ser positivo (tornando-se solúvel à luz) ou negativo (tornando-se insolúvel à luz), dependendo do processo específico.

- Aplicação da Máscara:

* A máscara é uma placa transparente ou semi-transparente contendo o padrão do circuito. Ela é posicionada com precisão sobre o resist por meio de sistemas de alinhamento avançados, garantindo a correspondência perfeita entre a máscara e o padrão desejado.

- Exposição à Luz:

* No decorrer da fase de exposição, a luz ultravioleta é precisamente direcionada para o resist por meio das áreas transparentes na máscara. As moléculas do resist expostas passam por uma transformação química, resultando em sua tornar-se solúvel (no caso do resist positivo) ou insolúvel (no caso do resist negativo) em solventes específicos. Esse processo é conduzido por um equipamento especializado denominado foto-alinhadora, responsável por realizar o alinhamento preciso da máscara e do substrato durante a exposição. Essa abordagem proporciona um controle aprimorado, garantindo uma reprodutibilidade máxima e, por conseguinte, alcançando maior resolução e precisão. Este nível de controle é particularmente crítico, dada a escala minúscula dos padrões, que estão na ordem de micrômetros. A foto-alinhadora desempenha, assim, um papel fundamental na asseguração de resultados consistentes e na obtenção de detalhes extremamente refinados na fabricação de dispositivos semicondutores.

- Desenvolvimento:

* O substrato é imerso em um solvente apropriado, revelando as áreas onde o resist foi alterado pela luz. O processo de desenvolvimento remove seletivamente as partes do resist que foram expostas, revelando padrões precisos do circuito na camada fotossensível.

- Transferência para o Substrato:

* As áreas agora expostas do substrato passam por etapas adicionais, como deposição de camadas condutoras (como alumínio ou cobre) ou isolantes (como dióxido de silício), conforme necessário para construir o circuito. Métodos como deposição química de vapor (CVD) e sputtering são comuns nesta fase.

- Repetição do Processo:

* O ciclo de fotolitografia é repetido para criar camadas adicionais, empilhando componentes e interconectando-os conforme necessário. Cada repetição adiciona complexidade e funcionalidade ao dispositivo final, construindo camadas de transistores, capacitores, diodos, fotodetetores e outros elementos essenciais.

- Desafios e Inovações:

* A constante miniaturização dos componentes eletrônicos apresenta desafios significativos, como a difração de luz em escalas nanométricas. Inovações, como a litografia de raios-X e a EUV, utilizam comprimentos de onda mais curtos para superar essas limitações, permitindo a criação de padrões ainda menores e mais complexos.

- Impacto na Tecnologia:

* A evolução da fotolitografia é central para a revolução digital. Ao possibilitar a fabricação de dispositivos eletrônicos cada vez menores, mais rápidos e mais eficientes, ela impulsiona avanços em áreas como inteligência artificial, internet das coisas (IoT) e comunicações sem fio. A fotolitografia é um alicerce fundamental para a inovação tecnológica, permitindo o desenvolvimento contínuo de dispositivos semicondutores avançados.