Arquitetura Harvard: diferenças entre revisões

m |

|||

| Linha 2: | Linha 2: | ||

[[File:Harvard architecture.svg|thumb|300px|Harvard architecture]] |

[[File:Harvard architecture.svg|thumb|300px|Harvard architecture]] |

||

A {{PU-AO45|Arquitetura de Harvard|Arquitectura de Harvard}} baseia-se em um conceito mais recente que a de Von-Neumann, tendo vindo da necessidade de por o [[microcontrolador]] para trabalhar mais rápido. É uma [[arquitetura de computador]] que se distingue das outras por possuir duas memórias diferentes e independentes em termos de [[barramento]] e ligação ao [[processador]]. É utilizada nos microcontroladores PIC, tem como principal característica acessar a memória de dados separadamente da memória de programa. |

A {{PU-AO45|Arquitetura de Harvard|Arquitectura de Harvard}} baseia-se em um conceito mais recente que a de Von-Neumann, tendo vindo da necessidade de por o [[microcontrolador]] para trabalhar mais rápido. É uma [[arquitetura de computador]] que se distingue das outras por possuir duas memórias diferentes e independentes em termos de [[barramento]] e ligação ao [[processador]]. É utilizada nos microcontroladores PIC, tem como principal característica acessar a memória de dados separadamente da memória de programa.<ref>[http://www.inf.pucrs.br/~emoreno/undergraduate/CC/orgarqi/class_files/Aula17/Aula17b.pdf Arquiteturas Von Neumann e Harvard]</ref><ref>Aurélien Francillon , Claude Castelluccia, Code Injection Attacks on Harvard-Architecture Devices (2009) {{DOI|10.1145/1455770.1455775}}</ref><ref> Daniel F. McCarthy , Architectures for parallel DSP-based adaptive optics feedback control {{DOI:10.1117/12.367581}}</ref><ref>Sid Katzen, '''The Essential PIC18® Microcontroller'''; Springer Science & Business Media, 2010, ISBN 1-849-96229-4</ref> |

||

Baseada também na separação de barramentos de dados das memórias onde estão as instruções de programa e das memórias de dados, permitindo que um processador possa acessar as duas simultaneamente, obtendo um desempenho melhor do que a da [[Arquitetura de von Neumann]], pois pode buscar uma nova instrução enquanto executa outra. |

Baseada também na separação de barramentos de dados das memórias onde estão as instruções de programa e das memórias de dados, permitindo que um processador possa acessar as duas simultaneamente, obtendo um desempenho melhor do que a da [[Arquitetura de von Neumann]], pois pode buscar uma nova instrução enquanto executa outra.<ref>[http://www.ijser.org/researchpaper%5CDesign-Synthesis-and-FPGA-based-Implementation-of-a-32-bit-Digital-Signal-Processor.pdf Design, Synthesis and FPGA - based Implementation of a 32 - bit Digital Signal Processor]</ref><ref> SHARC: Fast and Robust Unidirectional Routing , {{DOI| DOI:10.1137/1.9781611972887.2}}</ref> |

||

A principal vantagem dessa arquitetura é que a leitura de instruções e de alguns tipos de operandos pode ser feita ao mesmo tempo em que a execução das instruções (tempo Tcy). Isso significa que o sistema fica todo o tempo executando instruções, o que acarreta um significativo ganho de velocidade. Enquanto uma instrução está sendo executada, a seguinte está sendo lida. Esse processo é conhecido como [[pipeline (hardware)|pipelining]] (canalização). |

A principal vantagem dessa arquitetura é que a leitura de instruções e de alguns tipos de operandos pode ser feita ao mesmo tempo em que a execução das instruções (tempo Tcy). Isso significa que o sistema fica todo o tempo executando instruções, o que acarreta um significativo ganho de velocidade. Enquanto uma instrução está sendo executada, a seguinte está sendo lida. Esse processo é conhecido como [[pipeline (hardware)|pipelining]] (canalização). |

||

| Linha 29: | Linha 29: | ||

== História == |

== História == |

||

As raízes da arquitetura Harvard se originam na [[Universidade de Harvard]] com o projeto do computador [[Harvard Mark I]] que foi criado entre 1937 a 1944, durante a [[II Guerra Mundial]], idealizado por [[Howard Aiken]] com o apoio da [[IBM]] e da [[Marinha dos Estados Unidos|marinha norte americana]] foi considerado o primeiro projeto de computador. Utilizava muitas válvulas, as operações internas eram controladas por relés e os cálculos eram realizados mecanicamente. Integrava conceitos de computadores [[Computador digital|digitais]] e [[Computador analógico|analógicos]], pois tinha sistema [[eletrônico]] e [[mecânico]] na mesma máquina. |

As raízes da arquitetura Harvard se originam na [[Universidade de Harvard]] com o projeto do computador [[Harvard Mark I]] que foi criado entre 1937 a 1944, durante a [[II Guerra Mundial]], idealizado por [[Howard Aiken]] com o apoio da [[IBM]] e da [[Marinha dos Estados Unidos|marinha norte americana]] foi considerado o primeiro projeto de computador. Utilizava muitas válvulas, as operações internas eram controladas por relés e os cálculos eram realizados mecanicamente. Integrava conceitos de computadores [[Computador digital|digitais]] e [[Computador analógico|analógicos]], pois tinha sistema [[eletrônico]] e [[mecânico]] na mesma máquina.<ref> Cléuzio Fonseca Filho, '''História da computação: O Caminho do Pensamento e da Tecnologia'''; EDIPUCRS, ISBN 8-574-30691-6</ref> |

||

H. Aiken, o pesquisador que desenvolveu Mark I, construiu outras versões deste computador. Apesar de ter se originado do Mark I, a arquitetura Harvard só foi novamente impulsionada a partir da década de 70 com a criação de circuitos integrados por diversas empresas do segmento como a Signetics, que criou o dispositivo 8x300, a intel com o 8048, a General Instrumentspara uso como interface controladora de periféricos (PIC) que foi projetada para compensar o fraco barramento de I/O da sua CPU CP1600 de 16 bits. |

H. Aiken, o pesquisador que desenvolveu Mark I, construiu outras versões deste computador. Apesar de ter se originado do Mark I, a arquitetura Harvard só foi novamente impulsionada a partir da década de 70 com a criação de circuitos integrados por diversas empresas do segmento como a Signetics, que criou o dispositivo 8x300, a intel com o 8048, a General Instrumentspara uso como interface controladora de periféricos (PIC) que foi projetada para compensar o fraco barramento de I/O da sua CPU CP1600 de 16 bits. |

||

| Linha 49: | Linha 49: | ||

== Detalhes da memória == |

== Detalhes da memória == |

||

Na arquitetura de Harvard, não é necessário usar as duas memórias, pois possuem características em comum. Em especial, a largura da palavra, o tempo, tecnologia, implementação e estrutura de endereço de memória pode ser diferente. Em alguns sistemas, as instruções podem ser armazenadas na memória somente como leitura, enquanto a memória de dados geralmente requer leitura e escrita de memória. Em alguns sistemas, há mais memórias de dados para endereços de instrução do que memórias de instruções, pos são mais amplas do que os endereços de dados. |

Na arquitetura de Harvard, não é necessário usar as duas memórias, pois possuem características em comum. Em especial, a largura da palavra, o tempo, tecnologia, implementação e estrutura de endereço de memória pode ser diferente. Em alguns sistemas, as instruções podem ser armazenadas na memória somente como leitura, enquanto a memória de dados geralmente requer leitura e escrita de memória. Em alguns sistemas, há mais memórias de dados para endereços de instrução do que memórias de instruções, pos são mais amplas do que os endereços de dados.<ref>Kristopher Watts, Paul Oman, Stack-Based Buffer Overflows in Harvard Class Embedded Systems, pp 185-197 2009 {{DOI|10.1007/978-3-642-04798-5_13}} ISBN 978-3-642-04797-8 Online ISBN 978-3-642-04798-5</ref> |

||

==Comparando a Arquitetura de Harvard com a Arquitetura de Von Neumann== |

==Comparando a Arquitetura de Harvard com a Arquitetura de Von Neumann== |

||

| Linha 59: | Linha 59: | ||

Sobre a arquitetura de von Neumann a CPU pode ser uma instrução de leitura, escrita de dados de memória, ou para memória. Ambas as instruções, não podem ocorrer ao mesmo tempo, uma vez que as instruções e os dados fazem o uso do sistema de barramento. Em um computador que utiliza a arquitetura Harvard, a CPU pode ler uma instrução e executar um acesso à memória de dados ao mesmo tempo, mesmo sem cache, pode assim ser mais rápido para um circuito de complexidade dada porque a instrução busca o acesso a dados, sem acontecer por uma via única de memória. |

Sobre a arquitetura de von Neumann a CPU pode ser uma instrução de leitura, escrita de dados de memória, ou para memória. Ambas as instruções, não podem ocorrer ao mesmo tempo, uma vez que as instruções e os dados fazem o uso do sistema de barramento. Em um computador que utiliza a arquitetura Harvard, a CPU pode ler uma instrução e executar um acesso à memória de dados ao mesmo tempo, mesmo sem cache, pode assim ser mais rápido para um circuito de complexidade dada porque a instrução busca o acesso a dados, sem acontecer por uma via única de memória. |

||

Além disso, uma máquina que faz o uso da arquitetura de Harvard, tem o código, e espaços distintos, dados de endereço: o endereço da instrução zero não é o mesmo que os dados de endereço zero. A instrução do endereço zero pode identificar um valor de 24 bits, enquanto os dados de endereço zero pode indicar um byte de oito bits que não faz parte desse valor do bit 24. |

Além disso, uma máquina que faz o uso da arquitetura de Harvard, tem o código, e espaços distintos, dados de endereço: o endereço da instrução zero não é o mesmo que os dados de endereço zero. A instrução do endereço zero pode identificar um valor de 24 bits, enquanto os dados de endereço zero pode indicar um byte de oito bits que não faz parte desse valor do bit 24.<ref>{{DOI|01.IJEPE.02.02.44}}</ref> |

||

== {{Ver também}} == |

|||

{{div col}} |

|||

* [[Conjunto de instruções]] |

|||

{{div col end}} |

|||

{{Referências}} |

|||

{{Tecnologias de CPU}} |

{{Tecnologias de CPU}} |

||

{{Commons|Harvard architecture}} |

|||

{{Portal|Tecnologias de informação}} |

|||

{{Portal3|Tecnologias de informação}} |

{{Portal3|Tecnologias de informação}} |

||

{{esboço-informática}} |

{{esboço-informática}} |

||

{{DEFAULTSORT:Arquitetura Harvard}} |

|||

[[Categoria:Arquitetura de computadores]] |

[[Categoria:Arquitetura de computadores]] |

||

[[Categoria:Tipos de computadores]] |

[[Categoria:Tipos de computadores]] |

||

Revisão das 21h20min de 13 de dezembro de 2014

Este artigo não cita fontes confiáveis. (Janeiro de 2009) |

A Arquitetura de Harvard (AO 1945: Arquitectura de Harvard) baseia-se em um conceito mais recente que a de Von-Neumann, tendo vindo da necessidade de por o microcontrolador para trabalhar mais rápido. É uma arquitetura de computador que se distingue das outras por possuir duas memórias diferentes e independentes em termos de barramento e ligação ao processador. É utilizada nos microcontroladores PIC, tem como principal característica acessar a memória de dados separadamente da memória de programa.[1][2][3][4]

Baseada também na separação de barramentos de dados das memórias onde estão as instruções de programa e das memórias de dados, permitindo que um processador possa acessar as duas simultaneamente, obtendo um desempenho melhor do que a da Arquitetura de von Neumann, pois pode buscar uma nova instrução enquanto executa outra.[5][6]

A principal vantagem dessa arquitetura é que a leitura de instruções e de alguns tipos de operandos pode ser feita ao mesmo tempo em que a execução das instruções (tempo Tcy). Isso significa que o sistema fica todo o tempo executando instruções, o que acarreta um significativo ganho de velocidade. Enquanto uma instrução está sendo executada, a seguinte está sendo lida. Esse processo é conhecido como pipelining (canalização).

A arquitetura Havard também possui um repertório com menos instruções que a de Von-Neumann, e essas são executadas apenas num único ciclo de relógio.

Arquiteturas de Harvard são normalmente utilizadas em qualquer sistemas especializados ou para usos específicos. É utilizado em processamento de sinal digital especializados (DSP), normalmente por produtos de áudio e vídeo de transformação. Ele também é usado em muitos pequenos microcontroladores utilizados em aplicações eletrônicas, tais como máquinas RISCO Advanced (ARM) para produtos à base de muitos vendedores.

Os microcontroladores com arquitetura Havard são também conhecidos como "microcontroladores RISC" (Computador com Conjunto Reduzido de Instruções), e os microcontroladores com uma arquitetura Von-Neumann, de "microcontroladores CISC" (Computador com um Conjunto Complexo de Instruções).

RISC

Reduced Instruction Set Computer ou Computador com um Conjunto Reduzido de Instruções (RISC), é uma linha de arquitetura de processadores que favorece um conjunto simples e pequeno de instruções que levam aproximadamente a mesma quantidade de tempo para serem executadas. A maioria dos microprocessadores modernos são RISCs, por exemplo DEC Alpha, SPARC, MIPS, e PowerPC. O tipo de microprocessador mais largamente usado em desktops, o x86, é mais CISC do que RISC, embora chips mais novos traduzam instruções x86 baseadas em arquitetura CISC em formas baseadas em arquitetura RISC mais simples, utilizando prioridade de execução.

Os processadores baseados na computação de conjunto de instruções reduzido não tem micro-programação, as instruções são executadas diretamente pelo hardware. Como característica, esta arquitetura, além de não ter microcódigo, tem o conjunto de instruções reduzido, bem como baixo nível de complexidade. A idéia foi inspirada pela descoberta de que muitas das características incluídas na arquitetura tradicional de processadores para ganho de desempenho foram ignoradas pelos programas que foram executados neles. Mas o desempenho do processador em relação à memória que ele acessava era crescente. Isto resultou num número de técnicas para otimização do processo dentro do processador, enquanto ao mesmo tempo tentando reduzir o número total de acessos à memória. RISC é também a arquitetura adotada para os processadores dos jogos de video modernos, que proporcionam um hardware extremamente dedicado somente à execução do jogo, tornando-o muito mais rápido em relação a micro computadores com mais recursos, embora com processador x86.

CISC

CISC (sigla para Complex Instruction Set Computer, ou, em uma tradução literal, "Computador com um Conjunto Complexo de Instruções"): é uma linha de arquitetura de processadores capaz de executar centenas de instruções complexas diferentes sendo, assim, extremamente versátil. Exemplos de processadores CISC são os 386 e os 486 da Intel.

Os processadores baseados na computação de conjunto de instruções complexas contêm uma microprogramação, ou seja, um conjunto de códigos de instruções que são gravados no processador, permitindo-lhe receber as instruções dos programas e executá-las, utilizando as instruções contidas na sua microprogramação. Seria como quebrar estas instruções, já em baixo nível, em diversas instruções mais próximas do hardware (as instruções contidas no microcódigo do processador). Como característica marcante esta arquitetura contém um conjunto grande de instruções, a maioria deles em um elevado grau de complexidade. Examinando do ponto de vista um pouco mais prático, a vantagem da arquitetura CISC é que já temos muitas das instruções guardadas no próprio processador, o que facilita o trabalho dos programadores de linguagem de máquina; disponibilizando, assim, praticamente todas as instruções que serão usadas em seus programas. Os processadores CISC têm a vantagem de reduzir o tamanho do código executável por já possuirem muito do código comum em vários programas, em forma de uma única instrução. Porém, do ponto de vista da performance, os CISC's têm algumas desvantagens em relação aos RISC's, entre elas a impossibilidade de se alterar alguma instrução composta para se melhorar a performance. O código equivalente às instruções compostas do CISC pode ser escrito nos RISC's da forma desejada, usando um conjunto de instruções simples, da maneira que mais se adequar. Sendo assim, existe uma disputa entre tamanho do código X desempenho.

História

As raízes da arquitetura Harvard se originam na Universidade de Harvard com o projeto do computador Harvard Mark I que foi criado entre 1937 a 1944, durante a II Guerra Mundial, idealizado por Howard Aiken com o apoio da IBM e da marinha norte americana foi considerado o primeiro projeto de computador. Utilizava muitas válvulas, as operações internas eram controladas por relés e os cálculos eram realizados mecanicamente. Integrava conceitos de computadores digitais e analógicos, pois tinha sistema eletrônico e mecânico na mesma máquina.[7]

H. Aiken, o pesquisador que desenvolveu Mark I, construiu outras versões deste computador. Apesar de ter se originado do Mark I, a arquitetura Harvard só foi novamente impulsionada a partir da década de 70 com a criação de circuitos integrados por diversas empresas do segmento como a Signetics, que criou o dispositivo 8x300, a intel com o 8048, a General Instrumentspara uso como interface controladora de periféricos (PIC) que foi projetada para compensar o fraco barramento de I/O da sua CPU CP1600 de 16 bits. A divisão de microeletrônica foi depois transformada na Arizona Microchip Technology (por volta de 1985), com os PICs como seu produto principal, etc... Antes disso, a arquitetura Harvard tinha sido apenas uma curiosidade científica desde a sua invenção pela Universidade de Harvard.

Numa competição criada pelo departamento de Defesa que colocou Princeton contra Harvard, Princeton ganhou a competição porque o tempo médio entre falhas (MTBF) da sua arquitetura de memória mais simples era muito melhor, embora mais lenta que a proposta de Harvard. Com o desenvolvimento dos transistores e dos circuitos integrados, a arquitetura Harvard finalmente foi reconhecida. A Microchip fez melhoramentos na arquitetura original, e atualizou os blocos funcionais do projeto original com avanços modernos que estão em compasso com os processos arquitetônicos existentes e capacitados pelo baixo custo dos semicondutores.

Arquitetura de Harvard modificada

A Arquitectura de Harvard Modificada é uma variação da Arquitetura de Harvard que permite que o conteúdo da memória de programa seja acedido como se fosse memória de dados, esta é a principal diferença entre as duas arquiteturas. Quase todos os PCs modernos, que são estados de ser Harvard Architecture são realmente Modificado em Harvard Architecture.

Exemplos da arquiteura Harvard Modificada:

Acesso de leitura - os valores dados iniciais podem ser copiados da memória de instruções para a memória de dados quando um programa é iniciado.

Acesso de gravação - a capacidade de reprogramar é geralmente exigida; muito poucos computadores são meramente memória apenas para leitura (ROM) com base. Por exemplo um microcontrolador normalmente tem a capacidade de gravar a memória flash, que é usado para manter as suas instruções.

Detalhes da memória

Na arquitetura de Harvard, não é necessário usar as duas memórias, pois possuem características em comum. Em especial, a largura da palavra, o tempo, tecnologia, implementação e estrutura de endereço de memória pode ser diferente. Em alguns sistemas, as instruções podem ser armazenadas na memória somente como leitura, enquanto a memória de dados geralmente requer leitura e escrita de memória. Em alguns sistemas, há mais memórias de dados para endereços de instrução do que memórias de instruções, pos são mais amplas do que os endereços de dados.[8]

Comparando a Arquitetura de Harvard com a Arquitetura de Von Neumann

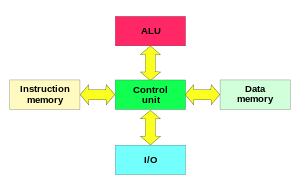

A diferença entre a arquitetura de Von Neunmann e a Harvard é que a última separa o armazenamento e o comportamento das instruções do CPU e os dados, enquanto a anterior utiliza o mesmo espaço de memória para ambos. Nos CPUs atuais, é mais comum encontrar a arquitetura Von Neunmann, mas algumas coisas da arquitetura Harvard também são vistas. Nessas distintas arquiteturas, temos vantagens e desvantagens, como pode-se observar a seguir: Arquitetura tipo Harvard: Caminhos de dados e de instrução distintos, dessa forma, seus componentes internos têm a seguinte disposição. Já na arquitetura Von-Neumann, é processada uma única informação por vez, visto que nessa tecnologia, execução e dados percorrem o mesmo barramento, o que torna o processo lento em relação à arquitetura Harvard. A arquitetura Harvard é mais utilizada nos microcontroladores, pois proporcionam maior velocidade de processamento, pois enquanto a CPU processa uma informação, outra nova informação está sendo buscada, de forma sucessiva.

Sobre a arquitetura de von Neumann a CPU pode ser uma instrução de leitura, escrita de dados de memória, ou para memória. Ambas as instruções, não podem ocorrer ao mesmo tempo, uma vez que as instruções e os dados fazem o uso do sistema de barramento. Em um computador que utiliza a arquitetura Harvard, a CPU pode ler uma instrução e executar um acesso à memória de dados ao mesmo tempo, mesmo sem cache, pode assim ser mais rápido para um circuito de complexidade dada porque a instrução busca o acesso a dados, sem acontecer por uma via única de memória.

Além disso, uma máquina que faz o uso da arquitetura de Harvard, tem o código, e espaços distintos, dados de endereço: o endereço da instrução zero não é o mesmo que os dados de endereço zero. A instrução do endereço zero pode identificar um valor de 24 bits, enquanto os dados de endereço zero pode indicar um byte de oito bits que não faz parte desse valor do bit 24.[9]

Ver também

Referências

- ↑ Arquiteturas Von Neumann e Harvard

- ↑ Aurélien Francillon , Claude Castelluccia, Code Injection Attacks on Harvard-Architecture Devices (2009) doi:10.1145/1455770.1455775

- ↑ Daniel F. McCarthy , Architectures for parallel DSP-based adaptive optics feedback control {{DOI:10.1117/12.367581}}

- ↑ Sid Katzen, The Essential PIC18® Microcontroller; Springer Science & Business Media, 2010, ISBN 1-849-96229-4

- ↑ Design, Synthesis and FPGA - based Implementation of a 32 - bit Digital Signal Processor

- ↑ SHARC: Fast and Robust Unidirectional Routing , doi:DOI:10.1137/1.9781611972887.2 DOI:10.1137/1.9781611972887.2

- ↑ Cléuzio Fonseca Filho, História da computação: O Caminho do Pensamento e da Tecnologia; EDIPUCRS, ISBN 8-574-30691-6

- ↑ Kristopher Watts, Paul Oman, Stack-Based Buffer Overflows in Harvard Class Embedded Systems, pp 185-197 2009 doi:10.1007/978-3-642-04798-5_13 ISBN 978-3-642-04797-8 Online ISBN 978-3-642-04798-5

- ↑ doi:01.IJEPE.02.02.44