Memória de acesso aleatório

A memória de acesso randômico(pt-BR) ou de acesso aleatório(pt-PT?) (do inglês Random Access Memory, conhecido pela abreviatura RAM),[1] também chamado de memória volátil de leitura e escrita, é uma memória temporária computacional de acesso rápido; ou seja, é um local de armazenamento temporário de informações digitais usada pelo processador para armazenar informações temporariamente e que possui um acesso feito de forma aleatória mais rápido que ao HD, DVD, pendrive (permite a rápida leitura e escrita de informações),[1][2] utilizada como memória primária em sistemas eletrônicos digitais.[3] O termo acesso aleatório permite acessar qualquer informação armazenada em qualquer momento.

A RAM é um componente essencial vários tipos de dispositivos, como: computador pessoal, computador servidor, smartphone, pois é onde basicamente ficam armazenados os programas básicos operacionais. Por mais que exista espaço de armazenamento disponível, na forma de um HDD, SSD ou memória flash, é sempre necessária uma certa quantidade de RAM.

O termo acesso aleatório identifica a capacidade de se ter acesso a qualquer posição e em qualquer momento, por oposição ao acesso sequencial imposto por alguns dispositivos de armazenamento, como fitas magnéticas. O nome não é verdadeiramente apropriado, já que outros tipos de memória (como a ROM) também permitem o acesso aleatório a seu conteúdo. O nome mais apropriado seria: Memória de Leitura e Escrita, que está expressa na programação computacional.

Apesar do conceito de memória operacional de acesso aleatório ser bastante amplo, atualmente o termo é usado apenas para definir um dispositivo eletrônico que o implementa, uma vez que atualmente essa memória se encontra espalhada dentro do próprio sistema dos atuais computadores (sistema por assim dizer "nervoso" do computador, como o humano), basicamente um tipo específico de chip. Nesse caso, também fica implícito que é uma memória volátil, todo o seu conteúdo é perdido quando a alimentação da memória é desligada. A memória principal de um computador baseado na Arquitetura de Von-Neumann é constituída por RAM. É nesta memória que são carregados os programas em execução e os respectivos dados do utilizador. Uma vez que se trata de memória volátil, os seus dados são perdidos quando o computador é desligado. Para evitar perdas de dados, é necessário salvar a informação para suporte não volátil, como o disco rígido.[4]

É usada pelo processador para armazenar os arquivos e programas que estão sendo processados. A quantidade de RAM disponível tem um grande efeito sobre o desempenho, já que sem uma quantidade suficiente dela o sistema passa a usar memória virtual, que é lenta. A principal característica da RAM é que ela é volátil, ou seja, os dados se perdem ao reiniciar o computador. Ao ligar é necessário refazer todo o processo de carregamento, em que o sistema operacional e aplicativos usados são transferidos do HD para a memória, onde podem ser executados pelo processador.[5]

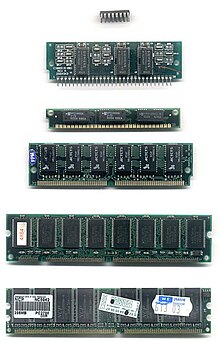

Os chips de memória são vendidos na forma de pentes de memória. Existem pentes de várias capacidades, e normalmente as placas possuem dois ou três encaixes disponíveis. Há como instalar um pente de 1 GB junto com o de 512 MB que veio no micro para ter um total de 1 536 MB, por exemplo.[5]

DRAM e SRAM

[editar | editar código-fonte]DRAM: modelo de memória RAM chamada "memória dinâmica de acesso remoto" (do inglês Dynamic Random Acess Memory). É dinâmica pois usa a atualização constante para manter os dados ativos (usa refresh).[1]

SRAM: modelo de memória RAM chamada "memória estática de acesso aleatório" (do inglês Static Random Acess Memory).[1] Um modelo que não usa a atualização constante ativar os dados (não usa refresh), tornando-se muito mais rápida que a DRAM.[1]

História

[editar | editar código-fonte]

Os primeiros computadores usavam relés, contadores mecânicos ou linhas de atraso para funções de memória principal.[6] As linhas de atraso ultrassônicas eram dispositivos seriais que só podiam reproduzir dados na ordem em que foram gravados. A memória do tambor poderia ser expandida a um custo relativamente baixo, mas a recuperação eficiente de itens de memória exigia conhecimento do layout físico do tambor para otimizar a velocidade. Travas construídas a partir de triodos de tubo de vácuo e, mais tarde, de transistores discretos, foram usadas para memórias menores e mais rápidas, como registradores. Esses registros eram relativamente grandes e muito caros para usar em grandes quantidades de dados; geralmente apenas algumas dezenas ou poucas centenas de bits dessa memória podem ser fornecidos.

A primeira forma prática de memória de acesso aleatório foi o tubo de Williams a partir de 1947. Ele armazenava dados como pontos eletricamente carregados na face de um tubo de raios catódicos. Como o feixe de elétrons do CRT podia ler e escrever os pontos no tubo em qualquer ordem, a memória era de acesso aleatório. A capacidade do tubo Williams era de algumas centenas a cerca de mil bits, mas era muito menor, mais rápido e mais eficiente em termos de energia do que usar travas individuais de tubo de vácuo. Desenvolvido na Universidade de Manchester, na Inglaterra, o tubo Williams forneceu o meio no qual o primeiro programa armazenado eletronicamente foi implementado no computador Manchester Baby, que primeiro executou um programa com sucesso em 21 de junho de 1948. sendo projetado para o bebê, o bebê foi um teste para demonstrar a confiabilidade da memória.

A memória de núcleo magnético foi inventada em 1947 e desenvolvida até meados da década de 1970. Tornou-se uma forma difundida de memória de acesso aleatório, contando com uma matriz de anéis magnetizados. Alterando o sentido da magnetização de cada anel, os dados podem ser armazenados com um bit armazenado por anel. Como cada anel tinha uma combinação de fios de endereço para selecioná-lo e lê-lo ou escrevê-lo, o acesso a qualquer local de memória em qualquer sequência era possível. A memória de núcleo magnético era a forma padrão de sistema de memória de computador até ser substituída pela memória semicondutora de estado sólido MOS (metal-óxido-silício) em circuitos integrados (ICs) durante o início da década de 1970.

Antes do desenvolvimento de circuitos integrados de memória somente leitura (ROM), a memória de acesso aleatório permanente (ou somente leitura) era frequentemente construída usando matrizes de diodo acionadas por decodificadores de endereço ou planos de memória de corda de núcleo especialmente enrolados.

A memória de semicondutores começou na década de 1960 com a memória bipolar, que usava transistores bipolares. Embora melhorasse o desempenho, não poderia competir com o preço mais baixo da memória de núcleo magnético.

Tipos

[editar | editar código-fonte]

Existem basicamente dois tipos de memória de acesso aleatório em uso: SDR e DDR. As SDRs são o tipo tradicional, onde o controlador de memória realiza apenas uma leitura por ciclo, enquanto as DDR são mais rápidas, pois fazem duas leituras por ciclo. O desempenho não chega a dobrar, pois o acesso inicial continua demorando o mesmo tempo, mas melhora bastante. Os pentes de memória SDR são usados em micros antigos: Pentium II e Pentium III e os primeiros Athlons e Durons soquete A. Por não serem mais fabricados, eles são atualmente muito mais raros e caros que os DDR, algo semelhante ao que aconteceu com os antigos pentes de 72 vias, usados na época do Pentium 1.[5]

É fácil diferenciar os pentes SDR e DDR, pois os SDR possuem dois chanfros e os DDR apenas um. Essa diferença faz com que também não seja possível trocar as bolas, encaixando por engano um pente DDR numa placa-mãe que use SDR e vice-versa. Mais recentemente, tem acontecido a uma nova migração, com a introdução dos pentes de memória DDR2. Neles, o barramento de acesso à memória trabalha ao dobro da frequência dos chips de memória propriamente ditos. Isso permite que sejam realizadas duas operações de leitura por ciclo, acessando dois endereços diferentes. Como a capacidade de realizar duas transferências por ciclo introduzida nas memórias DDR foi preservada, as memórias DDR2 são capazes de realizar um total de 4 operações de leitura por ciclo, uma marca impressionante. Existem ainda alguns ganhos secundários, como o menor consumo elétrico, útil em notebooks.[5]

Os pentes de memória DDR2 são incompatíveis com as placas-mãe antigas. Eles possuem um número maior de contatos (um total de 240, contra 184 dos pentes DDR), e o chanfro central é posicionado de forma diferente, de forma que não seja possível instalá-los nas placas antigas por engano. Muitos pentes são vendidos com um dissipador metálico, que ajuda na dissipação do calor e permite que os módulos operem a frequências mais altas.[5]

Os pentes de memória DDR3 tem o dobro de taxa de transferência se comparado ao DDR2. A tensão caiu de 1,8V da memória DDR2 para 1,5 V para a DDR3

O tipo DDR3 tem a mesma percepção da DDR2, com melhorias na qual dobra a quantidade de operações por vez em relação ao padrão anterior, ou seja, realiza 8 procedimentos de leitura ou gravação a cada ciclo de clock, quatro no início deste e outros quatro no final.

Geralmente são encontradas com chips que utilizam encapsulamento CSP (Chip Scale Package) com encaixes FBGA (Fine pitch Ball Grid Array), cuja principal característica é o fato de os terminais do chip serem pequenas soldas. A vantagem disso é que o sinal elétrico flui mais facilmente e há menos chances de danos físicos.

Capacidade e Velocidade

[editar | editar código-fonte]A capacidade de uma memória é medida em Bytes, Kilobyte (1 KB = 1 024 ou 210 Bytes), Megabyte (1 MB = 1 024 KB ou 220 Bytes), Gigabyte (1 GB = 1 024 MB ou 230 Bytes) e Terabyte (1 TB = 1 024 GB ou 2 40 Bytes).[7]

A velocidade de funcionamento de uma memória é medida em Hz ou MHz. Este valor está relacionado com a quantidade de blocos de dados que podem ser transferidos durante um segundo. Existem no entanto algumas RAMs que podem efetuar duas transferências de dados no mesmo ciclo de clock, duplicando a taxa de transferência de informação para a mesma frequência de trabalho. Além disso, a colocação das memórias em paralelo (propriedade da arquitetura de certos sistemas) permite multiplicar a velocidade aparente da memória.

Memória cache

[editar | editar código-fonte]

De qualquer forma, apesar de toda a evolução, a RAM continua sendo muito mais lenta que o processador. Para atenuar a diferença, são usados dois níveis de memória do tipo cache, incluídos no próprio processador: o cache L1 e o cache L2. O cache L1 é extremamente rápido, trabalhando próximo à frequência nativa do processador. Na verdade, os dois trabalham na mesma frequência, mas são necessários alguns ciclos de clock para que a informação armazenada no L1 chegue até as unidades de processamento. No caso do Pentium 4, chega-se ao extremo de armazenar instruções já decodificadas no L1: elas ocupam mais espaço, mas eliminam este tempo inicial. De uma forma geral, quanto mais rápido o cache, mais espaço ele ocupa e menos é possível incluir no processador. É por isso que o Pentium 4 inclui apenas um total de 20 KB desse cache L1 ultrarrápido, contra os 128 KB do cache um pouco mais lento usado no Sempron.[5]

Em seguida vem o cache L2, que é um pouco mais lento tanto em termos de tempo de acesso (o tempo necessário para iniciar a transferência) quanto em largura de banda, mas é bem mais econômico em termos de transistores, permitindo que seja usado em maior quantidade. O volume de cache L2 usado varia muito de acordo com o processador. Enquanto a maior parte dos modelos do Sempron utilizam apenas 256 KB, os modelos mais caros do Core 2 Duo possuem 4 MB completos.[5]

- Paridade de memória

É um método criado para correção de erros de memória. É o método mais antigo, e somente identifica erros, não os corrige, e consiste na adição de um bit de controle no final de cada byte de memória.

A operação de checagem dos dados na paridade é bem simples: são contados o número de bits “1” de cada byte. Se o número for par, o bit de paridade assume um valor “0” e caso seja ímpar, 9º bit assume um valor “1”. Quando requisitados pelo processador, os dados são checados pelo circuito de paridade que verifica se o número de bits “1” corresponde ao depositado no 9º bit. Caso seja constatada alteração nos dados, ele envia ao processador uma mensagem de erro.

O método não é totalmente eficaz, pois não é capaz de detectar a alteração de um número de bits que mantenha a paridade. Se dois bits zero retornassem alterados para bits um, o circuito de paridade não notaria a alteração nos dados. Felizmente, a possibilidade de alteração de dois ou mais bits ao mesmo tempo é remota.

O uso da paridade não torna o computador mais lento, pois os circuitos responsáveis pela checagem dos dados são independentes do restante do sistema. Seu único efeito colateral, é o encarecimento das memórias, que ao invés de 8 bits por byte, passam a ter 9, tornando-se cerca de 12 a 60% mais caras.

Dispositivo ECC-(Error Correct Code) - Código de correção de erros. Código de detecção no qual uma combinação de pulsos proibitiva pelo acréscimo ou perda de 1 bit indica qual bit esta errado.

Além do custo, a paridade não permite corrigir os erros, apenas identificá-los, o que diminui sua utilidade prática. O aumento do bom nível de confiabilidade dos novos módulos de memórias fez com que as memórias com paridade caíssem em desuso.

Ver também

[editar | editar código-fonte]Bibliografia

[editar | editar código-fonte]- Daniel Saraiva, J.E. MEMÓRIA ARTIFICIAL Editora Biblioteca da Universidade de oxford, 2000.

Referências

- ↑ a b c d e «Muito além da memória RAM; o que é DRAM e SRAM?». Tecnoblog. Consultado em 5 de junho de 2024

- ↑ «Memórias: RAM e ROM». WebEduc. Ministério da Educação do Brasil (MEC). Consultado em 29 de junho de 2022

- ↑ Equipe Baixaki (11 de novembro de 2008). «O que é memória RAM?». Tec Mundo. Consultado em 5 de janeiro de 2012

- ↑ Carlos E. Morimoto (1 de janeiro de 2012). «Capítulo 3: Memória RAM». Guia do Hardware. Consultado em 5 de janeiro de 2012

- ↑ a b c d e f g Guia do Hardware. «Memória RAM». Consultado em 9 de janeiro de 2012. Arquivado do original em 12 de agosto de 2010

- ↑ eduCAPES. «eduCAPES» (PDF)

- ↑ QSL. «Entenda a Memória do seu Computador». Consultado em 9 de janeiro de 2012. Arquivado do original em 4 de dezembro de 2008