PCI Express

| PCI Express | |

|---|---|

| Ano de criação: | |

| 2003 | |

| Criado por | |

| Substitui | |

| Largura em bits | |

| 1 por pista (até 16 pistas) | |

| Nº de dispositivos | |

| 1 em ada terminal de cada conexão.[nota 1] | |

| Velocidade | |

Dual simplex (em cada direção); exemplos em pista única (x1) e 16 pistas (x16):

| |

| Estilo | |

| Serial | |

| Interface de Hotplug | |

| Sim (com ExpressCard, OCuLink, CFexpress ou U.2) | |

| Interface externa | |

| Sim (com cabeamento externo OCuLink ou PCI Express) | |

| Site oficial | |

| pcisig.com/ |

- PCI Express x4

- PCI Express x16

- PCI Express x1

- PCI Express X16

- PCI convencional (32 bits, 5 V)

PCI Express (Peripheral Component Interconnect Express), oficialmente abreviado como PCIe ou PCI-e,[1] é um padrão de barramento de expansão de computador serial de alta velocidade, projetado para substituir os antigos padrões de barramento PCI, PCI-X e AGP. É a interface de placa-mãe usual para placas gráficas de computadores pessoais, controladores de disco rígido, SSDs, conexões de hardware Wi-Fi e Ethernet.[2] O PCIe tem inúmeras melhorias em relação aos padrões mais antigos, incluindo maior taxa de transferência máxima do barramento do sistema, menor contagem de pinos de E/S e menor espaço físico, melhor dimensionamento de desempenho para dispositivos de barramento, um mecanismo de detecção e relatório de erros mais detalhado (Relatório avançado de erros, AER),[3] e funcionalidade nativa de hot swap. Revisões mais recentes do padrão PCIe fornecem suporte de hardware para virtualização de E/S.

A interface elétrica PCI Express é medida pelo número de pistas simultâneas.[4] (Uma pista é uma única linha de envio/recebimento de dados. A analogia é uma rodovia com tráfego em ambas as direções.) A interface também é usada em vários outros padrões - mais notavelmente na interface de placa de expansão de laptop chamada ExpressCard. Também é usado nas interfaces de armazenamento de Sata Express, U.2 (SFF-8639) e M.2.

As especificações de formato são mantidas e desenvolvidas pelo PCI-SIG (PCI Special Interest Group) - um grupo de mais de 900 empresas que também mantém as especificações convencionais do PCI.

Arquitetura

[editar | editar código-fonte]

as "caixas de junção" brancas representam as portas downstream do dispositivo PCI Express, enquanto as cinzas representam as portas upstream.[5]:7

Conceitualmente, o barramento PCI Express é uma substituição serial de alta velocidade do antigo barramento PCI/PCI-X.[7] Uma das principais diferenças entre o barramento PCI Express e o PCI mais antigo é a topologia do barramento; O PCI usa uma arquitetura de barramento paralelo compartilhado, na qual o host PCI e todos os dispositivos compartilham um conjunto comum de endereços, dados e linhas de controle. Em contraste, o PCI Express é baseado na topologia ponto a ponto, com links seriais separados conectando cada dispositivo ao complexo raiz(hospedeiro). Por causa de sua topologia de barramento compartilhado, o acesso ao barramento PCI mais antigo é arbitrado (no caso de vários mestres) e limitado a um mestre por vez, em uma única direção. Além disso, o esquema de clock PCI mais antigo limita o clock do barramento ao periférico mais lento no barramento (independentemente dos dispositivos envolvidos na transação do barramento). Em contraste, um link de barramento PCI Express suporta comunição full-duplex entre quaisquer dois terminais, sem limitação inerente ao acesso simultâneo em vários terminais.

Em termos de protocolo de barramento, a comunicação PCI Express é encapsulada em pacotes. O trabalho de empacotamento e desempacotamento de dados e tráfego de mensagens de status é tratado pela camada de transação da porta PCI Express (descrita posteriormente). Diferenças radicais na sinalização elétrica e no protocolo de barramento exigem o uso de um fator de forma mecânico diferente e conectores de expansão (e, portanto, novas placas-mãe e novas placas adaptadoras); Os slots PCI e os slots PCI Express não são intercambiáveis. No nível do software, o PCI Express preserva a compatibilidade com o PCI; software de sistema PCI legado pode detectar e configurar dispositivos PCI Express mais recentes sem suporte explícito para o padrão PCI Express, embora os novos recursos PCI Express sejam inacessíveis.

O link PCI Express entre dois dispositivos pode variar em tamanho de uma a 16 pistas. Em um link de várias vias, os dados do pacote são distribuídos pelas vias e a taxa de transferência de dados de pico é dimensionada com a largura geral do link. A contagem de pistas é negociada automaticamente durante a inicialização do dispositivo e pode ser restringida por qualquer ponto final. Por exemplo, uma placa PCI Express de pista única (x1) pode ser inserida em um slot de várias pistas (x4, x8, etc.), e o ciclo de inicialização negocia automaticamente a contagem mais alta de pistas mutuamente suportadas. O link pode se configurar dinamicamente para usar menos pistas, fornecendo uma tolerância a falhas caso haja pistas ruins ou não confiáveis. O padrão PCI Express define larguras de link de x1, x2, x4, x8 e x16. Até e incluindo os links PCIe 5.0, x12 e x32 também foram definidos, mas nunca usados.[8] Isso permite que o barramento PCI Express atenda tanto a aplicativos de custo-benefício onde não é necessária alta taxa de transferência, quanto a aplicativos de desempenho crítico, como gráficos 3D, rede (10 Gigabit Ethernet ou Gigabit Ethernet multiporta) e armazenamento corporativo (SAS e Fibre channel). Slots e conectores são definidos apenas para um subconjunto dessas larguras, com larguras de link intermediárias usando o próximo tamanho de slot físico maior.

Como ponto de referência, um dispositivo PCI-X (133 MHz 64 bits) e um dispositivo PCI Express 1.0 usando quatro pistas (x4) têm aproximadamente a mesma taxa de transferência de direção única de pico de 1064 MB/s. O barramento PCI Express tem o potencial de ter um desempenho melhor do que o barramento PCI-X nos casos em que vários dispositivos estão transferindo dados simultaneamente ou se a comunicação com o periférico PCI Express for bidirecional.

Interconexão

[editar | editar código-fonte]

Os dispositivos PCI Express se comunicam por meio de uma conexão lógica chamada de interconexão[9] ou link. Um link é um canal de comunicação ponto a ponto entre duas portas PCI Express permitindo que ambas enviem e recebam solicitações PCI comuns (configuração, E/S ou leitura/gravação de memória) e interrupções (INTx, MSI ou MSI-X). No nível físico, um link é composto por uma ou mais pistas.[9] Periféricos de baixa velocidade (como uma placa Wi-Fi 802.11) usam um link de pista única (x1), enquanto um adaptador gráfico normalmente usa um link de 16 pistas (x16) muito mais amplo e, portanto, mais rápido.

Linha

[editar | editar código-fonte]Uma pista é composta por dois pares de sinalização diferencial, sendo um par para recepção de dados e outro para transmissão. Assim, cada pista é composta por quatro fios ou traços de sinal. Conceitualmente, cada pista é usada como um fluxo de bytes full-duplex, transportando pacotes de dados em formato "byte" de oito bits simultaneamente em ambas as direções entre os terminais de um link.[10] Os links físicos PCI Express podem conter 1, 4, 8 ou 16 vias.[11][5]:4,5[9] As contagens de pistas são escritas com um prefixo "x" (por exemplo, "x8" representa um cartão ou slot de oito pistas), sendo x16 o maior tamanho de uso comum.[12] [13] Os tamanhos das pistas também são referidos pelos termos "largura" ou "por", por exemplo, um slot de oito pistas pode ser referido como "por 8" ou como "8 pistas de largura".

Para tamanhos de cartões mecânicos, veja abaixo.

Barramento serial

[editar | editar código-fonte]A arquitetura de barramento serial vinculado foi escolhida em relação ao barramento paralelo tradicional devido às limitações inerentes deste último, incluindo operação half-duplex, contagem de sinal em excesso e largura de banda inerente menor devido à distorção de tempo. A distorção de tempo resulta de sinais elétricos separados dentro de uma interface paralela viajando através de condutores de diferentes comprimentos, em camadas de placas de circuito impresso (PCB) potencialmente diferentes e em velocidades de sinal possivelmente diferentes. Apesar de ser transmitido simultaneamente como uma única palavra, os sinais em um interface paralela têm diferentes durações de viagem e chegam aos seus destinos em momentos diferentes. Quando o período de clock da interface é menor que a maior diferença de tempo entre as chegadas do sinal, a recuperação da palavra transmitida não é mais possível. Como a distorção de tempo em um barramento paralelo pode chegar a alguns nanossegundos, a limitação de larguda de banda resultante está na faixa de centenas de megahertz.

Uma interface serial não exibe distorção de tempo porque há apenas um sinal diferencial em cada direção dentro de cada pista e não há sinal de clock externo, pois as informações de clock estão incorporadas no próprio sinal serial. Como tal, as limitações típicas de largura de banda em sinais seriais estão na faixa de vários gigahertz. PCI Express é um exemplo da tendência geral de substituir barramentos paralelos por interconexões seriais; outros exemplos incluem Serial ATA (SATA), USB, Serial Attached SCSI (SAS), FireWire (IEEE 1394) e RapidIO. Em vídeo digital, exemplos de uso comum são DVI, HDMI e DisplayPort.

O design serial multicanal aumenta a flexibilidade com sua capacidade de alocar menos pistas para dispositivos mais lentos.

Fatores de forma

[editar | editar código-fonte]PCI Express (padrão)

[editar | editar código-fonte]

Uma placa PCI Express cabe em um slot de seu tamanho físico ou maior (com x16 como o maior usado), mas pode não caber em um slot PCI Express menor; por exemplo, um cartão x16 pode não caber em um slot x4 ou x8. Alguns slots usam soquetes abertos para permitir cartões fisicamente mais longos e negociar a melhor conexão elétrica e lógica disponível.

O número de pistas realmente conectadas a um slot também pode ser menor do que o número suportado pelo tamanho do slot físico. Um exemplo é um slot x16 executado em x4, que aceita qualquer placa x1, x2, x4, x8 ou x16, mas fornece apenas quatro pistas. Sua especificação pode ser lida como "x16 (modo x4)", enquanto a notação "mecânica @ elétrica" (por exemplo, "x16 @ x4") também é comum.[carece de fontes] A vantagem é que tais slots podem acomodar uma gama maior de placas PCI Express sem exigir hardware da placa-mãe para suportar a taxa de transferência total. Os tamanhos mecânicos padrão são x1, x4, x8 e x16. Cartões com um número diferente de pistas precisam usar o próximo tamanho mecânico maior (ou seja, um cartão x2 usa o tamanho x4 ou um cartão x12 usa o tamanho x16).

Os próprios cartões são projetados e fabricados em vários tamanhos. Por exemplo, unidades de estado sólido (SSDs) que vêm na forma de placas PCI Express geralmente usam HHHL (meia altura, metade do comprimento) e FHHL (altura total, metade do comprimento) para descrever as dimensões físicas da placa.[14][15]

| Tipo de placa PCI | Dimensões altura × comprimento × largura, máximo | |

|---|---|---|

| milímetros (mm) | dentro | |

| Comprimento total | 111.15 × 312.00 × 20.32 | 4.376 × 12.283 × 0.8 |

| Metade do comprimento | 111.15 × 167.65 × 20.32 | 4.376 × 6.600 × 0.8 |

| Perfil baixo/fino | 68.90 × 167.65 × 20.32 | 2.731 × 6.600 × 0.8 |

Fatores de forma de placa de vídeo não padrão

[editar | editar código-fonte]Placas de vídeo para jogos modernas (desde c.2012[16]) geralmente excedem a altura e a espessura especificadas no padrão PCI Express, devido à necessidade de ventoinhas de resfriamento mais capazes e mais silenciosas, pois as placas de vídeo para jogos geralmente emitem centenas de watts de calor.[17] Os gabinetes de computadores modernos geralmente são mais largos para acomodar esses cartões mais altos, mas nem sempre. Como os cartões de comprimento total (312 mm) são incomuns, os estojos modernos às vezes não podem caber neles. A espessura dessas placas também normalmente ocupa o espaço de 2 slots PCIe. De fato, até mesmo a metodologia de como medir os cartões varia entre os fornecedores, com alguns incluindo o tamanho do suporte de metal nas dimensões e outros não.

Por exemplo, uma placa Sapphire 2020 mede 135 de largura (excluindo o suporte de metal), que excede a altura padrão PCIe em 28 mm.[18] Outra placa da XFX mede 55 mm de espessura (ou seja, 2,7 slots PCI a 20,32 mm), ocupando 3 slots PCIe.[19] A placa de vídeo Asus GeForce RTX 3080 10 GB STRIX GAMING OC é uma placa de dois slots que possui dimensões de 318,5 mm × 140,1 mm × 57,8 mm, excedendo o comprimento, altura e espessura máximos do PCI Express, respectivamente.[20]

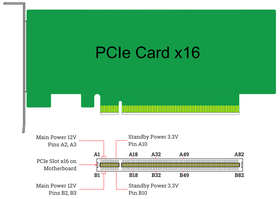

Pinagem

[editar | editar código-fonte]A tabela a seguir identifica os condutores em cada lado do slot em uma placa PCI Express. O lado da solda da placa de circuito impresso (PCB) é o lado A e o lado do componente é o lado B.[21] Os pinos PRSNT1# e PRSNT2# devem ser um pouco mais curtos do que os demais, para garantir que um cartão hot plug seja totalmente inserido. O pino WAKE# usa voltagem total para ativar o computador, mas deve ser puxado para cima da energia de espera para indicar que a placa é capaz de ativar.[22]

| Pino | Lado B | Lado A | Descrição | Pino | Lado B | Lado A | Descrição | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12 V | PRSNT1# | Deve se conectar ao pino PRSNT2# mais distante | 50 | HSOp(8) | Reservado | A pista 8 transmite dados, + e - | |

| 2 | +12 V | +12 V | Pinos de alimentação principal | 51 | HSOn(8) | Ground | ||

| 3 | +12 V | +12 V | 52 | Ground | HSIp(8) | A pista 8 recebe dados, + e - | ||

| 4 | Ground | Ground | 53 | Ground | HSIn(8) | |||

| 5 | SMCLK | TCK | Pinos de porta SMBus e JTAG | 54 | HSOp(9) | Ground | A pista 9 transmite dados, + e - | |

| 6 | SMDAT | TDI | 55 | HSOn(9) | Ground | |||

| 7 | Ground | TDO | 56 | Ground | HSIp(9) | A pista 9 recebe dados, + e - | ||

| 8 | +3.3 V | TMS | 57 | Ground | HSIn(9) | |||

| 9 | TRST# | +3.3 V | 58 | HSOp(10) | Ground | A pista 10 transmite dados, + e - | ||

| 10 | +3.3 V aux | +3.3 V | Stand by | 59 | HSOn(10) | Ground | ||

| 11 | WAKE# | PERST# | Reativação de links; reset fundamental[carece de fontes] | 60 | Ground | HSIp(10) | A pista 10 recebe dados, + e - | |

| Entalhe chave | 61 | Ground | HSIn(10) | |||||

| 12 | CLKREQ#[23] | Ground | Sinal de solicitação de clock | 62 | HSOp(11) | Ground | A pista 11 transmite dados, + e - | |

| 13 | Ground | REFCLK+ | Par diferencial de clock de referência | 63 | HSOn(11) | Ground | ||

| 14 | HSOp(0) | REFCLK− | A pista 0 transmite dados, + e - | 64 | Ground | HSIp(11) | A pista 11 recebe dados, + e - | |

| 15 | HSOn(0) | Ground | 65 | Ground | HSIn(11) | |||

| 16 | Ground | HSIp(0) | A pista 0 recebe dados, + e - | 66 | HSOp(12) | Ground | A pista 12 transmite dados, + e - | |

| 17 | PRSNT2# | HSIn(0) | 67 | HSOn(12) | Ground | |||

| 18 | Ground | Ground | 68 | Ground | HSIp(12) | A pista 12 recebe dados, + e - | ||

| As placas PCI Express x1 terminam no pino 18 | 69 | Ground | HSIn(12) | |||||

| 19 | HSOp(1) | Reservado | A pista 1 transmite dados, + e - | 70 | HSOp(13) | Ground | A pista 13 transmite dados, + e - | |

| 20 | HSOn(1) | Ground | 71 | HSOn(13) | Ground | |||

| 21 | Ground | HSIp(1) | A pista 1 recebe dados, + e - | 72 | Ground | HSIp(13) | A pista 13 recebe dados, + e - | |

| 22 | Ground | HSIn(1) | 73 | Ground | HSIn(13) | |||

| 23 | HSOp(2) | Ground | A pista 2 transmite dados, + e - | 74 | HSOp(14) | Ground | A pista 14 transmite dados, + e - | |

| 24 | HSOn(2) | Ground | 75 | HSOn(14) | Ground | |||

| 25 | Ground | HSIp(2) | A pista 2 recebe dados, + e - | 76 | Ground | HSIp(14) | A pista 14 recebe dados, + e - | |

| 26 | Ground | HSIn(2) | 77 | Ground | HSIn(14) | |||

| 27 | HSOp(3) | Ground | A pista 3 transmite dados, + e - | 78 | HSOp(15) | Ground | A pista 15 transmite dados, + e - | |

| 28 | HSOn(3) | Ground | 79 | HSOn(15) | Ground | |||

| 29 | Ground | HSIp(3) | A pista 3 recebe dados, + e - | 80 | Ground | HSIp(15) | A pista 15 recebe dados, + e - | |

| 30 | PWRBRK#[24] | HSIn(3) | 81 | PRSNT2# | HSIn(15) | |||

| 31 | PRSNT2# | Ground | 82 | Reservado | Ground | |||

| 32 | Ground | Reservado | ||||||

| As placas PCI Express x4 terminam no pino 32 | ||||||||

| 33 | HSOp(4) | Reservado | A pista 4 transmite dados, + e - | |||||

| 34 | HSOn(4) | Ground | ||||||

| 35 | Ground | HSIp(4) | A pista 4 recebe dados, + e - | |||||

| 36 | Ground | HSIn(4) | ||||||

| 37 | HSOp(5) | Ground | A pista 5 transmite dados, + e - | |||||

| 38 | HSOn(5) | Ground | ||||||

| 39 | Ground | HSIp(5) | A pista 5 recebe dados, + e - | |||||

| 40 | Ground | HSIn(5) | ||||||

| 41 | HSOp(6) | Ground | A pista 6 transmite dados, + e - | |||||

| 42 | HSOn(6) | Ground | ||||||

| 43 | Ground | HSIp(6) | A pista 6 recebe dados, + e - | Legenda | ||||

| 44 | Ground | HSIn(6) | Pino Ground (GND) | Referência zero volt | ||||

| 45 | HSOp(7) | Ground | A pista 7 transmite dados, + e - | Pino de alimentação | Fornece energia para a placa PCIe | |||

| 46 | HSOn(7) | Ground | Pino do cartão para o host | Sinal do cartão para a placa-mãe | ||||

| 47 | Ground | HSIp(7) | A pista 7 recebe dados, + e - | Pino do host para o cartão | Sinal da placa-mãe para o cartão | |||

| 48 | PRSNT2# | HSIn(7) | Dreno aberto | Pode ser baixado ou detectado por vários cartões | ||||

| 49 | Ground | Ground | Pino de detecção | Amarrados juntos no cartão | ||||

| As placas PCI Express x8 terminam no pino 49 | Reservado | Não usado atualmente, não conecte | ||||||

Power

[editar | editar código-fonte]

Todas as placas PCI Express podem consumir 3A em +3,3 V (9,9 W). A quantidade de +12 V e a potência total que podem consumir depende do fator de forma e da função do cartão:[25]:35–36[26][27]

- placas x1 são limitadas a 0,5 A a +12 V (6 W) e 10 W combinados.

- x4 e placas mais amplas são limitadas a 2,1 A a +12 V (25 W) e 25 W combinados.

- Um cartão x1 de tamanho normal pode consumir até os limites de 25 W após a inicialização e a configuração do software como um dispositivo de alta potência.

- Uma placa gráfica x16 de tamanho normal pode consumir até 5,5 A a +12 V (66 W) e 75 W combinados após a inicialização e configuração do software como um dispositivo de alta potência.[22]:38–39

Conectores opcionais adicionam 75 W (6 pinos) ou 150 W (8 pinos) de alimentação de +12V para até 300 W no total (2 × 75 W + 1 × 150 W).

- O pino Sense0 é conectado ao terra pelo cabo ou fonte de alimentação, ou flutua a bordo se o cabo não estiver conectado.

- O pino Sense1 é conectado ao terra pelo cabo ou fonte de alimentação, ou flutua a bordo se o cabo não estiver conectado.

Algumas placas usam dois conectores de 8 pinos, mas isso ainda não foi padronizado a partir de 2018, portanto, essas placas não devem levar o logotipo oficial do PCI Express. Esta configuração permite um total de 375 W (1 × 75 W + 2 × 150 W) e provavelmente será padronizada por PCI-SIG com o padrão PCI Express 4.0.[carece de fontes] O conector PCI Express de 8 pinos pode ser confundido com o conector EPS12V, que é usado principalmente para alimentar sistemas SMP e multi-core. Os conectores de alimentação são variantes dos conectores da série Molex Mini-Fit Jr..[29]

| Pinos | Fêmea/receptáculo no cabo PS |

Cabeçalho macho/ângulo reto no PCB |

|---|---|---|

| 6-pinos | 45559-0002 | 45558-0003 |

| 8-pinos | 45587-0004 | 45586-0005, 45586-0006 |

| Conector de alimentação de 6 pinos (75 W)[30] | Conector de alimentação de 8 pinos (150 W)[31][32][33] | ||||

|---|---|---|---|---|---|

| Pino | Descrição | Pino | Descrição | ||

| 1 | +12 V | 1 | +12 V | ||

| 2 | Não conectado (geralmente +12 V também) | 2 | +12 V | ||

| 3 | +12 V | 3 | +12 V | ||

| 4 | Sense1 (8 pinos conectado[A]) | ||||

| 4 | Ground | 5 | Ground | ||

| 5 | Sense | 6 | Sense0 (6 pinos ou 8 pinos conectados) | ||

| 6 | Ground | 7 | Ground | ||

| 8 | Ground | ||||

- ↑ Quando um conector de 6 pinos é conectado a um receptáculo de 8 pinos, a placa é notificada por um Sense1 ausente de que ela pode usar apenas até 75 W.

PCI Express Mini Card

[editar | editar código-fonte]

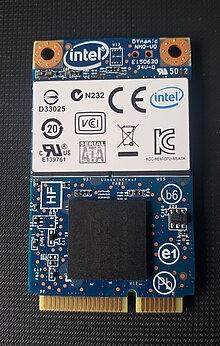

PCI Express Mini Card (também conhecido como Mini PCI Express, Mini PCIe, Mini PCI-E, mPCIe e PEM), baseado no PCI Express, é um substituto para o formato Mini PCI. É desenvolvido pelo PCI-SIG. O dispositivo host suporta conectividade PCI Express e USB 2.0, e cada placa pode usar qualquer um dos padrões. A maioria dos laptops construídos depois de 2005 usa PCI Express para placas de expansão; no entanto, a partir de 2015, muitos fornecedores estão adotando o formato M.2 mais recente para essa finalidade.

Devido às diferentes dimensões, as miniplacas PCI Express não são fisicamente compatíveis com slots PCI Express de tamanho normal; no entanto, existem adaptadores passivos que permitem que sejam usados em slots de tamanho normal.[34]

Dimensões físicas

[editar | editar código-fonte]As dimensões das miniplacas PCI Express são 30 mm × 50,95 mm (largura × comprimento) para uma miniplaca completa. Há um conector de borda de 52 pinos, que consiste em duas linhas escalonadas em um passo de 0,8 mm. Cada linha tem oito contatos, uma lacuna equivalente a quatro contatos e mais 18 contatos. As placas têm espessura de 1,0 mm, excluindo os componentes. Um "Half Mini Card" (às vezes abreviado como HMC) também é especificado, tendo aproximadamente metade do comprimento físico de 26,8 mm.

Interface elétrica

[editar | editar código-fonte]Os conectores de borda PCI Express Mini Card fornecem várias conexões e barramentos:

- PCI Express x1 (com SMBus)

- USB 2.0

- Fios para LEDs de diagnóstico para status de rede sem fio (ou seja, Wi-Fi) no chassi do computador

- Cartão SIM para aplicativos GSM e WCDMA (sinais UIM na especificação)

- Extensão futura para outra pista PCIe

- Alimentação de 1,5 V e 3,3 V

Variante Mini-SATA (mSATA)

[editar | editar código-fonte]

Apesar de compartilhar o formato Mini PCI Express, um slot mSATA não é necessariamente compatível eletricamente com o Mini PCI Express. Por esse motivo, apenas alguns notebooks são compatíveis com unidades mSATA. A maioria dos sistemas compatíveis são baseados na arquitetura do processador Sandy Bridge da Intel, usando a plataforma Huron River. Notebooks como as séries ThinkPad T, W e X da Lenovo, lançados em março-abril de 2011, têm suporte para um cartão SSD mSATA em seu slot de cartão WWAN. O ThinkPad Edge E220s/E420s e o Lenovo IdeaPad Y460/Y560/Y570/Y580 também suportam mSATA.[35] Pelo contrário, a série L, entre outras, só pode suportar placas M.2 usando o padrão PCIe no slot WWAN.

Alguns notebooks (principalmente o ASUS Eee PC, o Apple MacBook Air e o Dell mini9 e mini10) usam uma variante do PCI Express Mini Card como um SSD. Essa variante usa os pinos reservados e vários não reservados para implementar a passagem de interface SATA e IDE, mantendo apenas USB, linhas de aterramento e, às vezes, o barramento PCIe x1 principal intacto.[36] Isso torna as unidades flash e de estado sólido "miniPCIe" vendidas para netbooks amplamente incompatíveis com implementações verdadeiras de PCI Express Mini.

Além disso, o SSD miniPCIe típico da Asus tem 71 mm de comprimento, fazendo com que o modelo Dell de 51 mm seja muitas vezes (incorretamente) referido como meio comprimento. Um verdadeiro SSD Mini PCIe de 51 mm foi anunciado em 2009, com duas camadas de PCB empilhadas que permitem maior capacidade de armazenamento. O design anunciado preserva a interface PCIe, tornando-a compatível com o slot mini PCIe padrão. Nenhum produto funcional ainda foi desenvolvido.

A Intel tem várias desktop boards com slot PCIe x1 Mini-Card que normalmente não suportam SSD mSATA. Uma lista de desktop boards que suportam nativamente mSATA no slot PCIe x1 Mini-Card (normalmente multiplexadas com uma porta SATA) é fornecida no site de suporte da Intel.[37]

PCI Express M.2

[editar | editar código-fonte]M.2 substitui o padrão mSATA e Mini PCIe.[38] As interfaces de barramento de computador fornecidas através do conector M.2 são PCI Express 3.0 (até quatro vias), Serial ATA 3.0 e USB 3.0 (uma única porta lógica para cada uma das duas últimas). Cabe ao fabricante do host ou dispositivo M.2 escolher quais interfaces suportar, dependendo do nível desejado de suporte do host e do tipo de dispositivo.

Cabeamento externo PCI Express

[editar | editar código-fonte]Especificações de cabeamento externo PCI Express (também conhecido como PCI Express externo, PCI Express cabeado ou ePCIe) foram lançadas pelo PCI-SIG em fevereiro de 2007.[39][40]

Cabos e conectores padrão foram definidos para larguras de link x1, x4, x8 e x16, com uma taxa de transferência de 250 MB/s por pista. O PCI-SIG também espera que a norma evolua para atingir 500 MB/s, como no PCI Express 2.0. Um exemplo dos usos do Cabled PCI Express é um gabinete de metal, contendo vários slots PCIe e circuitos adaptadores PCIe-para-ePCIe. Este dispositivo não seria possível se não fosse pela especificação ePCIe.

PCI Express OCuLink

[editar | editar código-fonte]OCuLink (significa "link óptico-cobre", já que Cu é o símbolo químico para Cobre) é uma extensão para a "versão a cabo do PCI Express", atuando como concorrente da versão 3 da interface Thunderbolt. A versão 1.0 do OCuLink, lançada em outubro de 2015, suporta até PCIe 3.0 x4 lanes (8 GT/s (gigatransfers por segundo), 3,9 GB/s) em cabeamento de cobre; uma versão de fibra óptica pode aparecer no futuro.

Em sua versão mais recente, o OCuLink-2, ele suporta até 16 GB/s (PCIe 4.0 x8)[41] enquanto a largura de banda máxima de um cabo Thunderbolt 4 de velocidade total é de 5 GB/s. Alguns fornecedores podem projetar seu produto de conector para ser capaz de suportar PCI Express 5.0 de próxima geração rodando a 32 GT/s por pista para prova futura e minimizando os custos de desenvolvimento nos próximos anos.[41] Inicialmente, o PCI-SIG esperava trazer o OCuLink para laptops para conexão de poderosas caixas de GPU externas. Acabou sendo um uso raro. Em vez disso, o OCuLink tornou-se popular para interconexões PCIe em servidores.[42]

Formas derivadas

[editar | editar código-fonte]Vários outros fatores de forma usam ou podem usar PCIe. Esses incluem:

- Cartão de altura baixa

- ExpressCard: Sucessor do formato PC Card (com x1 PCIe e USB 2.0; hot-pluggable)

- PCI Express ExpressModule: Um fator de forma modular hot-pluggable definido para servidores e estações de trabalho

- Cartão XQD: Um padrão de cartão flash baseado em PCI Express pela CompactFlash Association com x2 PCIe

- Cartão CFexpress: Um cartão flash baseado em PCI Express da CompactFlash Association em três formatos que suportam 1 a 4 pistas PCIe

- Cartão SD: O barramento SD Express, introduzido na versão 7.0 da especificação SD, usa um link PCIe x1

- XMC: Semelhante ao fator de forma CMC/PMC (VITA 42.3)

- AdvancedTCA: Um complemento ao CompactPCI para aplicações maiores; suporta topologias de backplane baseadas em série

- AMC: Um complemento à especificação AdvancedTCA; suporta processadores e módulos de E/S em placas ATCA (x1, x2, x4 ou x8 PCIe).

- FeaturePak: Um pequeno formato de cartão de expansão (43 mm × 65 mm) para aplicativos incorporados e de fator de forma pequeno, que implementa dois links PCIe x1 em um conector de alta densidade junto com USB, I2C e até 100 pontos de I/O

- Universal IO: Uma variante da Super Micro Computer Inc projetada para uso em chassis montados em rack de baixo perfil. Ele tem o suporte do conector invertido para que não caiba em um soquete PCI Express normal, mas é compatível com pinos e pode ser inserido se o suporte for removido.

- M.2 (anteriormente conhecido como NGFF)

- O M-PCIe traz o PCIe 3.0 para dispositivos móveis (como tablets e smartphones), sobre a camada física do M-PHY.[43][44]

- U.2 (anteriormente conhecido como SFF-8639)

O conector do slot PCIe também pode transportar outros protocolos além do PCIe. Alguns chipsets Intel da série 9xx suportam Serial Digital Video Out, uma tecnologia proprietária que usa um slot para transmitir sinais de vídeo dos gráficos integrados da CPU host em vez de PCIe, usando um complemento compatível.

O protocolo de camada de transação PCIe também pode ser usado em algumas outras interconexões, que não são eletricamente PCIe:

- Thunderbolt: Um padrão de interconexão isento de royalties da Intel que combina os protocolos DisplayPort e PCIe em um formato compatível com Mini DisplayPort. O Thunderbolt 3.0 também combina USB 3.1 e usa o formato USB-C em oposição ao Mini DisplayPort.

- USB4

História e revisões

[editar | editar código-fonte]Enquanto no início do desenvolvimento, PCIe foi inicialmente referido como HSI (para High Speed Interconnect), e passou por uma mudança de nome para 3GIO (para E/S de 3ª Geração) antes de finalmente se estabelecer em seu nome PCI-SIG PCI Express. Um grupo de trabalho técnico chamado Arapaho Work Group (AWG) elaborou o padrão. Para os rascunhos iniciais, o AWG consistia apenas de engenheiros da Intel; posteriormente, o AWG se expandiu para incluir parceiros do setor.

Desde então, o PCIe passou por várias revisões grandes e menores, melhorando o desempenho e outros recursos.

| Versão | Introduzido | Código de linha | Taxa de transferência por pista[i][ii] |

Taxa de transferência[i][iii] | |||||

|---|---|---|---|---|---|---|---|---|---|

| x1 | x2 | x4 | x8 | x16 | |||||

| 1.0 | 2003 | NRZ | 8b/10b | 2.5 GT/s | 0.250 GB/s | 0.500 GB/s | 1.000 GB/s | 2.000 GB/s | 4.000 GB/s |

| 2.0 | 2007 | 5.0 GT/s | 0.500 GB/s | 1.000 GB/s | 2.000 GB/s | 4.000 GB/s | 8.000 GB/s | ||

| 3.0 | 2010 | 128b/130b | 8.0 GT/s | 0.985 GB/s | 1.969 GB/s | 3.938 GB/s | 7.877 GB/s | 15.754 GB/s | |

| 4.0 | 2017 | 16.0 GT/s | 1.969 GB/s | 3.938 GB/s | 7.877 GB/s | 15.754 GB/s | 31.508 GB/s | ||

| 5.0 | 2019 | 32.0 GT/s | 3.938 GB/s | 7.877 GB/s | 15.754 GB/s | 31.508 GB/s | 63.015 GB/s | ||

| 6.0 | 2022 | PAM-4 FEC |

242B/256B FLIT |

64.0 GT/s 32.0 GBd |

7.563 GB/s | 15.125 GB/s | 30.250 GB/s | 60.500 GB/s | 121.000 GB/s |

| 7.0 | 2025 (planejado) | 128.0 GT/s 64.0 GBd |

15.125 GB/s | 30.250 GB/s | 60.500 GB/s | 121.000 GB/s | 242.000 GB/s | ||

- Notas

- ↑ a b Em cada direção (cada pista é um canal dual simplex).

- ↑ A taxa de transferência refere-se à taxa de bits serial codificada; 2,5 GT/s significa taxa de dados serial de 2,5 Gbit/s.

- ↑ A taxa de transferência indica a largura de banda não codificada (sem sobrecarga de codificação 8b/10b, 128b/130b ou 242B/256B). A taxa de transferência PCIe 1.0 de 2,5 GT/s por pista significa uma taxa de bits serial de 2,5 Gbit/s correspondente a uma taxa de transferência de 2,0 Gbit/s ou 250 MB/s antes da codificação 8b/10b.

PCI Express 1.0a

[editar | editar código-fonte]

Em 2003, o PCI-SIG introduziu o PCIe 1.0a, com taxa de dados por pista de 250 MB/s e taxa de transferência de 2,5 gigatransfers por segundo (GT/s).

A taxa de transferência é expressa em transferências por segundo em vez de bits por segundo porque o número de transferências inclui os bits de sobrecarga, que não fornecem taxa de transferência adicional;[47] PCIe 1.x usa um esquema de codificação 8b/10b, resultando em uma sobrecarga de 20% (= 2/10) na largura de banda do canal bruto.[48] Assim, na terminologia PCIe, a taxa de transferência refere-se à taxa de bits codificada: 2,5 GT/s é 2,5 Gbps no link serial codificado. Isso corresponde a 2,0 Gbps de dados pré-codificados ou 250 MB/s, que é chamado de taxa de transferência no PCIe.

PCI Express 1.1

[editar | editar código-fonte]Em 2005, o PCI-SIG[49] introduziu o PCIe 1.1. Esta especificação atualizada inclui esclarecimentos e várias melhorias, mas é totalmente compatível com PCI Express 1.0a. Nenhuma alteração foi feita na taxa de dados.

PCI Express 2.0

[editar | editar código-fonte]

PCI-SIG anunciou a disponibilidade da especificação PCI Express Base 2.0 em 15 de janeiro de 2007.[50] O padrão PCIe 2.0 dobra a taxa de transferência em comparação com PCIe 1.0 a 5 GT/s e o throughput por pista aumenta de 250 MB/s a 500 MB/s. Consequentemente, um conector PCIe de 16 pistas (x16) pode suportar uma taxa de transferência agregada de até 8 GB/s.

Os slots da placa-mãe PCIe 2.0 são totalmente compatíveis com as placas PCIe v1.x. As placas PCIe 2.0 também são geralmente compatíveis com placas-mãe PCIe 1.x, usando a largura de banda disponível do PCI Express 1.1. Em geral, placas gráficas ou placas-mãe projetadas para funcionar na v2.0, sendo a outra v1.1 ou v1.0a.

O PCI-SIG também disse que o PCIe 2.0 apresenta melhorias no protocolo de transferência de dados ponto a ponto e sua arquitetura de software.[51]

O primeiro chipset compatível com PCIe 2.0 da Intel foi o X38 e as placas começaram a ser enviadas de vários fornecedores (Abit, Asus, Gigabyte) em 21 de outubro de 2007.[52] A AMD começou a suportar PCIe 2.0 com sua série de chipsets AMD 700 e a nVidia começou com o MCP72.[53] Todos os chipsets anteriores da Intel, incluindo o chipset Intel P35, suportavam PCIe 1.1 ou 1.0a.[54]

Assim como o 1.x, o PCIe 2.0 usa um esquema de codificação 8b/10b, portanto, entregando, por pista, um máximo efetivo de 4 Gbit/s. taxa de transferência de sua taxa de dados brutos de 5 GT/s.

PCI Express 2.1

[editar | editar código-fonte]O PCI Express 2.1 (com sua especificação datada de 4 de março de 2009) suporta uma grande parte dos sistemas de gerenciamento, suporte e solução de problemas planejados para implementação completa no PCI Express 3.0. No entanto, a velocidade é a mesma do PCI Express 2.0. O aumento na potência do slot quebra a compatibilidade com versões anteriores entre placas PCI Express 2.1 e algumas placas-mãe mais antigas com 1.0/1.0a, mas a maioria das placas-mãe com conectores PCI Express 1.1 é fornecida com uma atualização de BIOS por seus fabricantes por meio de utilitários para oferecer suporte à compatibilidade com versões anteriores de placas com PCIe 2.1.

PCI Express 3.0

[editar | editar código-fonte]A revisão 3.0 da especificação PCI Express 3.0 Base foi disponibilizada em novembro de 2010, após vários atrasos. Em agosto de 2007, o PCI-SIG anunciou que o PCI Express 3.0 teria uma taxa de bits de 8 gigatransfers por segundo (GT/s) e que seria compatível com as implementações PCI Express existentes. Naquela época, também foi anunciado que a especificação final para PCI Express 3.0 seria adiada até o segundo trimestre de 2010.[55] Novos recursos para a especificação PCI Express 3.0 incluíam uma série de otimizações para sinalização aprimorada e integridade de dados, incluindo transmissor e receptor equalização, melhorias de PLL, recuperação de dados de clock e aprimoramentos de canal de topologias atualmente suportadas.[56]

Após uma análise técnica de seis meses da viabilidade de dimensionar a largura de banda de interconexão PCI Express, a análise da PCI-SIG descobriu que 8 gigatransfers por segundo podem ser fabricadas em tecnologia de processo de silício convencional e implantadas com materiais e infraestrutura de baixo custo existentes, mantendo compatibilidade total (com impacto insignificante) com a pilha de protocolos PCI Express.

O PCI Express 3.0 atualizou o esquema de codificação para 128b/130b da codificação 8b/10b anterior, reduzindo a sobrecarga de largura de banda de 20% do PCI Express 2.0 para aproximadamente 1,54% (= 2/130). A taxa de bits de 8 GT/s do PCI Express 3.0 oferece efetivamente 985 MB/s por pista, quase dobrando a largura de banda da pista em relação ao PCI Express 2.0.[46]

Em 18 de novembro de 2010, o PCI Special Interest Group publicou oficialmente a especificação finalizada do PCI Express 3.0 para seus membros para construir dispositivos baseados nesta nova versão do PCI Express.[57]

PCI Express 3.1

[editar | editar código-fonte]Em setembro de 2013, a especificação PCI Express 3.1 foi anunciada para lançamento no final de 2013 ou início de 2014, consolidando várias melhorias na especificação PCI Express 3.0 publicada em três áreas: gerenciamento de energia, desempenho e funcionalidade.[44][58] Foi lançado em novembro de 2014.[59]

PCI Express 4.0

[editar | editar código-fonte]Em 29 de novembro de 2011, o PCI-SIG anunciou preliminarmente o PCI Express 4.0,[60] fornecendo uma taxa de bits de 16 GT/s que dobra a largura de banda fornecida pelo PCI Express 3.0 para 31,5 GB/s em cada direção para uma configuração de 16 pistas, enquanto mantendo a compatibilidade com versões anteriores e posteriores no suporte de software e na interface mecânica usada.[61] As especificações do PCI Express 4.0 também trazem o OCuLink-2, uma alternativa ao Thunderbolt. O OCuLink versão 2 tem até 16 GT/s (total de 16 GB/s para x8 pistas),[41] enquanto a largura de banda máxima de um link Thunderbolt 3 é de 5 GB/s.

Em junho de 2016, Cadence, PLDA e Synopsys demonstraram PCIe 4.0 de camada física, controlador, switch e outros blocos IP na conferência anual de desenvolvedores do PCI SIG.[62]

A Mellanox Technologies anunciou o primeiro adaptador de rede de 100 Gbit/s com PCIe 4.0 em 15 de junho de 2016,[63] e o primeiro adaptador de rede de 200 Gbit/s com PCIe 4.0 em 10 de novembro de 2016.[64]

Em agosto de 2016, a Synopsys apresentou uma configuração de teste com FPGA com clock de uma pista para velocidades PCIe 4.0 no Intel Developer Forum. Seu IP foi licenciado para várias empresas que planejam apresentar seus chips e produtos no final de 2016.[65]

No IEEE Hot Chips Symposium em agosto de 2016, a IBM anunciou a primeira CPU com suporte a PCIe 4.0, POWER9.[66][67]

A PCI-SIG anunciou oficialmente o lançamento da especificação final do PCI Express 4.0 em 8 de junho de 2017.[68] A especificação inclui melhorias na flexibilidade, escalabilidade e baixo consumo de energia.

Em 5 de dezembro de 2017, a IBM anunciou o primeiro sistema com slots PCIe 4.0, Power AC922.[69][70]

A NETINT Technologies apresentou o primeiro SSD NVMe baseado em PCIe 4.0 em 17 de julho de 2018, antes do Flash Memory Summit 2018.[71]

A AMD anunciou em 9 de janeiro de 2019 que seus próximos processadores baseados em Zen 2 e chipset X570 suportariam PCIe 4.0.[72] A AMD esperava habilitar suporte parcial para chipsets mais antigos, mas a instabilidade causada por rastros da placa-mãe que não estavam em conformidade com as especificações PCIe 4.0 tornou isso impossível.[73][74]

A Intel lançou suas primeiras CPUs móveis com suporte PCI express 4.0 em meados de 2020, como parte da microarquitetura Tiger Lake.[75]

PCI Express 5.0

[editar | editar código-fonte]Em junho de 2017, o PCI-SIG anunciou a especificação preliminar do PCI Express 5.0.[68] Esperava-se que a largura de banda aumentasse para 32 GT/s, produzindo 63 GB/s em cada direção em uma configuração de 16 pistas. Esperava-se que o projeto de especificação fosse padronizado em 2019.[carece de fontes] Inicialmente, 25,0 GT/s também foi considerado para viabilidade técnica.

Em 7 de junho de 2017 no PCI-SIG DevCon, a Synopsys registrou a primeira demonstração do PCI Express 5.0 a 32 GT/s.[76]

Em 31 de maio de 2018, a PLDA anunciou a disponibilidade de seu IP do controlador XpressRICH5 PCIe 5.0 com base no rascunho 0.7 da especificação PCIe 5.0 no mesmo dia.[77]

Em 10 de dezembro de 2018, o PCI SIG lançou a versão 0.9 da especificação PCIe 5.0 para seus membros,[78] e em 17 de janeiro de 2019, o PCI SIG anunciou que a versão 0.9 havia sido ratificada, com a versão 1.0 prevista para lançamento no primeiro trimestre de 2019.[79]

Em 29 de maio de 2019, o PCI-SIG anunciou oficialmente o lançamento da especificação final do PCI Express 5.0.[80]

Em 20 de novembro de 2019, a Jiangsu Huacun apresentou o primeiro controlador PCIe 5.0 HC9001 em um processo de fabricação de 12 nm.[81] A produção começou em 2020.

Em 17 de agosto de 2020, a IBM anunciou o processador POWER10 com PCIe 5.0 e até 32 pistas por módulo de chip único (SCM) e até 64 pistas por módulo de chip duplo (DCM).[82]

Em 9 de setembro de 2021, a IBM anunciou o servidor Power E1080 Enterprise com data de disponibilidade planejada para 17 de setembro.[83] Pode ter até 16 SCMs POWER10 com no máximo 32 slots por sistema que podem atuar como PCIe 5.0 x8 ou PCIe 4.0 x16.[84] Alternativamente, eles podem ser usados como slots PCIe 5.0 x16 para adaptadores conversores CXP ópticos opcionais conectados a gavetas de expansão PCIe externas.

Em 27 de outubro de 2021, a Intel anunciou a família de CPUs Intel Core de 12ª geração, os primeiros processadores x86-64 de consumo do mundo com conectividade PCIe 5.0 (até 16 pistas).[85]

Em 22 de março de 2022, a Nvidia anunciou a GPU Nvidia Hopper GH100, a primeira GPU PCIe 5.0 do mundo.[86]

Em 23 de maio de 2022, a AMD anunciou sua arquitetura Zen 4 com suporte para até 24 pistas de conectividade PCIe 5.0 em plataformas de consumo.[87]

PCI Express 6.0

[editar | editar código-fonte]Em 18 de junho de 2019, a PCI-SIG anunciou o desenvolvimento da especificação PCI Express 6.0. Espera-se que a largura de banda aumente para 64 GT/s, produzindo 128 GB/s em cada direção em uma configuração de 16 pistas, com uma data de lançamento prevista para 2021.[88] O novo padrão usa modulação de amplitude de pulso de 4 níveis (PAM -4) com uma correção de erro direta de baixa latência (FEC) no lugar da modulação sem retorno a zero (NRZ).[89] Ao contrário das versões anteriores do PCI Express, a correção de erros direta é usada para aumentar a integridade dos dados e o PAM-4 é usado como código de linha para que dois bits sejam transferidos por transferência. Com taxa de transferência de dados de 64 GT/s (taxa de bits brutos), até 121 GB/s em cada direção é possível na configuração x16.[88]

Em 24 de fevereiro de 2020, foi lançada a especificação PCI Express 6.0 revisão 0.5 (um "primeiro rascunho" com todos os aspectos arquitetônicos e requisitos definidos).[90]

Em 5 de novembro de 2020, foi lançada a especificação PCI Express 6.0 revisão 0.7 (um "rascunho completo" com especificações elétricas validadas por meio de chips de teste).[91]

Em 6 de outubro de 2021, a especificação PCI Express 6.0 revisão 0.9 (um "rascunho final") foi lançada.[92]

Em 11 de janeiro de 2022, o PCI-SIG anunciou oficialmente o lançamento da especificação final do PCI Express 6.0.[93]

A codificação PAM-4 resulta em uma taxa de erro de bits (BER) muito mais alta de 10 −6 (vs. 10 −12 anteriormente), portanto, no lugar da codificação 128b/130b, uma correção de erro direta entrelaçada de 3 vias (FEC) é usada além da verificação de redundância cíclica (CRC). Um bloco FLIT (Flow Control Unit) fixo de 256 bytes transporta 242 bytes de dados, que inclui pacotes de nível de transação (TLP) de tamanho variável e carga útil da camada de enlace de dados (DLLP); os 14 bytes restantes são reservados para CRC de 8 bytes e FEC de 6 bytes.[94][95] Código Gray de 3 vias é usado no modo PAM-4/FLIT para reduzir a taxa de erro; a interface não muda para a codificação NRZ e 128/130b mesmo ao retreinar para taxas de dados mais baixas.[96][97]

PCI Express 7.0

[editar | editar código-fonte]Em 21 de junho de 2022, a PCI-SIG anunciou o desenvolvimento da especificação PCI Express 7.0.[98] Ele fornecerá uma taxa de bits bruta de 128 GT/s e até 242 GB/s por direção na configuração x16, usando a mesma sinalização PAM4 da versão 6.0. A duplicação da taxa de dados será alcançada pelo ajuste fino dos parâmetros do canal para diminuir as perdas de sinal e melhorar a eficiência de energia. A especificação deve ser finalizada em 2025.

Extensões e direções futuras

[editar | editar código-fonte]Alguns fornecedores oferecem produtos PCIe sobre fibra,[99][100] com cabos ópticos ativos (AOC) para comutação PCIe a distância aumentada em gavetas de expansão PCIe,[101][84] ou em casos específicos onde a ponte PCIe é transparente é preferível usar um padrão mais convencional (como InfiniBand ou Ethernet) que pode exigir software adicional para suportá-lo.

Thunderbolt foi co-desenvolvido pela Intel e pela Apple como uma interface de uso geral de alta velocidade combinando um link PCIe lógico com DisplayPort e foi originalmente concebido como uma interface totalmente em fibra, mas devido a dificuldades iniciais na criação de uma interconexão de fibra amigável ao consumidor, quase todas as implementações são sistemas de cobre. Uma exceção notável, o Sony VAIO Z VPC-Z2, usa uma porta USB não padrão com um componente óptico para conectar a um adaptador de vídeo PCIe externo. A Apple tem sido o principal impulsionador da adoção do Thunderbolt até 2011, embora vários outros fornecedores[102] tenham anunciado novos produtos e sistemas com Thunderbolt. Thunderbolt 3 forma a base do USB4 padrão.

A especificação Mobile PCIe (abreviada para M-PCIe) permite que a arquitetura PCI Express opere sobre a tecnologia de camada física M-PHY da MIPI Alliance. Com base na ampla adoção já existente do M-PHY e seu design de baixo consumo de energia, o Mobile PCIe permite que os dispositivos móveis usem o PCI Express.[103]

Processo de rascunho

[editar | editar código-fonte]Existem 5 versões principais/pontos de verificação em uma especificação PCI-SIG:[104]

- Rascunho 0.3 (Conceito): esta versão pode ter poucos detalhes, mas descreve a abordagem geral e os objetivos.

- Rascunho 0.5 (Primeiro rascunho): esta versão possui um conjunto completo de requisitos de arquitetura e deve atender totalmente às metas estabelecidas no rascunho 0.3.

- Rascunho 0.7 (rascunho completo): esta versão deve ter um conjunto completo de requisitos funcionais e métodos definidos, e nenhuma nova funcionalidade pode ser adicionada à especificação após esta versão. Antes do lançamento deste projeto, as especificações elétricas devem ter sido validadas por meio de teste de silício.

- Rascunho 0.9 (rascunho final): esta versão permite que as empresas membros do PCI-SIG realizem uma revisão interna de propriedade intelectual, e nenhuma alteração funcional é permitida após esse rascunho.

- 1.0 (versão final): esta é a especificação final e definitiva, e quaisquer alterações ou aprimoramentos são por meio de documentação de errata e avisos de alteração de engenharia (ECNs), respectivamente.

Historicamente, os primeiros adotantes de uma nova especificação PCIe geralmente começam a projetar com o Rascunho 0.5, pois podem construir com confiança sua lógica de aplicativo em torno da nova definição de largura de banda e, muitas vezes, até mesmo começar a desenvolver para quaisquer novos recursos de protocolo. No estágio Rascunho 0.5, no entanto, ainda há uma forte probabilidade de mudanças na implementação real da camada de protocolo PCIe, portanto, os designers responsáveis por desenvolver esses blocos internamente podem hesitar mais em começar a trabalhar do que aqueles que usam IP de interface de fontes externas.

Resumo de protocolo de hardware

[editar | editar código-fonte]O link PCIe é construído em torno de pares unidirecionais dedicados de conexões seriais (1 bit), ponto a ponto, conhecidas como lanes. Isso contrasta fortemente com a conexão PCI anterior, que é um sistema baseado em barramento em que todos os dispositivos compartilham o mesmo barramento paralelo bidirecional de 32 bits ou 64 bits.

PCI Express é um protocolo em camadas, consistindo em uma camada de transação, uma camada de enlace de dados e uma camada física. A camada de enlace de dados é subdividida para incluir uma subcamada de controle de acesso ao meio (MAC). A camada física é subdividida em subcamadas lógicas e elétricas. A subcamada lógica física contém uma subcamada de codificação física (PCS). Os termos são emprestados do modelo de protocolo de rede IEEE 802.

Camada física

[editar | editar código-fonte]| Pistas | Pinos | Comprimento | ||

|---|---|---|---|---|

| Total | Variável | Total | Variável | |

| x1 | 2×18 = 36[105] | 2×7 = 14 | 25 mm | 7.65 mm |

| x4 | 2×32 = 64 | 2×21 = 42 | 39 mm | 21.65 mm |

| x8 | 2×49 = 98 | 2×38 = 76 | 56 mm | 38.65 mm |

| x16 | 2×82 = 164 | 2×71 = 142 | 89 mm | 71.65 mm |

A especificação PCIe Physical Layer (PHY, PCIEPHY, PCI Express PHY ou PCIe PHY) é dividida em duas subcamadas, correspondentes às especificações elétricas e lógicas. A subcamada lógica às vezes é dividida em subcamada MAC e PCS, embora essa divisão não seja formalmente parte da especificação PCIe. Uma especificação publicada pela Intel, a PHY Interface for PCI Express (PIPE),[106] define o particionamento funcional MAC/PCS e a interface entre essas duas subcamadas. A especificação PIPE também identifica a camada de anexo de mídia física (PMA), que inclui o serializador/desserializador (SerDes) e outros circuitos analógicos; entretanto, como as implementações do SerDes variam muito entre os fornecedores de ASIC, o PIPE não especifica uma interface entre o PCS e o PMA.

No nível elétrico, cada pista consiste em dois pares diferenciais unidirecionais operando a 2,5, 5, 8, 16 ou 32 Gbit/s, dependendo das capacidades negociadas. Transmissão e recepção são pares diferenciais separados, para um total de quatro fios de dados por pista.

Uma conexão entre quaisquer dois dispositivos PCIe é conhecida como link e é construída a partir de uma coleção de uma ou mais vias. Todos os dispositivos devem oferecer suporte mínimo ao link de pista única (x1). Os dispositivos podem, opcionalmente, suportar links mais amplos compostos por até 32 vias.[107][108] Isso permite uma compatibilidade muito boa de duas maneiras:

- Uma placa PCIe se encaixa fisicamente (e funciona corretamente) em qualquer slot que seja pelo menos tão grande quanto (por exemplo, uma placa de tamanho x1 funciona em qualquer slot de tamanho);

- Um slot de tamanho físico grande (por exemplo, x16) pode ser conectado eletricamente com menos pistas (por exemplo, x1, x4, x8 ou x12), desde que forneça as conexões de aterramento exigidas pelo tamanho do slot físico maior.

Em ambos os casos, o PCIe negocia o maior número de vias com suporte mútuo. Muitas placas gráficas, placas-mãe e versões de BIOS são verificadas para suportar conectividade x1, x4, x8 e x16 na mesma conexão.

A largura de um conector PCIe é de 8,8 mm, enquanto a altura é de 11,25 mm e o comprimento é variável. A seção fixa do conector tem 11,65 mm de comprimento e contém duas fileiras de 11 pinos cada (22 pinos no total), enquanto o comprimento da outra seção é variável dependendo do número de pistas. Os pinos são espaçados em intervalos de 1 mm e a espessura do cartão que entra no conector é de 1,6 mm.[109][110]

Transmissão de dados

[editar | editar código-fonte]O PCIe envia todas as mensagens de controle, incluindo interrupções, pelos mesmos links usados para dados. O protocolo serial nunca pode ser bloqueado, portanto, a latência ainda é comparável ao PCI convencional, que possui linhas de interrupção dedicadas. Quando o problema de compartilhamento de IRQ de interrupções baseadas em pinos é levado em consideração e o fato de que as interrupções sinalizadas por mensagem (MSI) podem contornar um APIC de E/S e serem entregues diretamente à CPU, o desempenho do MSI acaba sendo substancialmente melhor.[111]

Os dados transmitidos em links de várias vias são intercalados, o que significa que cada byte sucessivo é enviado por vias sucessivas. A especificação PCIe refere-se a essa intercalação como distribuição de dados. Embora exija uma complexidade de hardware significativa para sincronizar (ou deskew) os dados distribuídos de entrada, o striping pode reduzir significativamente a latência do n - ésimo byte em um link. Embora as pistas não estejam totalmente sincronizadas, há um limite para a inclinação pista a pista de 20/8/6 ns para 2,5/5/8 GT/s para que os buffers de hardware possam realinhar os dados distribuídos.[112] Devido aos requisitos de preenchimento, o striping pode não necessariamente reduzir a latência de pequenos pacotes de dados em um link.

Tal como acontece com outros protocolos de transmissão serial de alta taxa de dados, o clock está embutido no sinal. No nível físico, o PCI Express 2.0 utiliza o esquema de codificação 8b/10b[46] (código de linha) para garantir que sequências de dígitos idênticos consecutivos (zeros ou uns) sejam limitadas em comprimento. Essa codificação foi usada para evitar que o receptor perdesse o controle de onde estão as bordas dos bits. Nesse esquema de codificação, cada oito bits de dados de carga útil (não codificados) são substituídos por 10 bits (codificados) de dados de transmissão, causando uma sobrecarga de 20% na largura de banda elétrica. Para melhorar a largura de banda disponível, o PCI Express versão 3.0 usa a codificação 128b/130b (sobrecarga de 1,54%). Codificação de linha limita o comprimento de execução de sequências de dígitos idênticos em fluxos de dados e garante que o receptor permaneça sincronizado com o transmissor por meio da recuperação do clock.

Um equilíbrio desejável (e, portanto, densidade espectral) de 0 e 1 bits no fluxo de dados é obtido por [[Ou exclusivo|XORing] de um polinômio binário conhecido como um "embaralhador" para o fluxo de dados em uma topologia de realimentação. Como o polinômio de embaralhamento é conhecido, os dados podem ser recuperados aplicando o XOR uma segunda vez. As etapas de codificação e decodificação são realizadas em hardware.

Camada de enlace de dados

[editar | editar código-fonte]A camada de link de dados executa três serviços vitais para o link PCIe:

- sequenciar os pacotes da camada de transação (TLPs) que são gerados pela camada de transação,

- garantir a entrega confiável de TLPs entre dois terminais por meio de um protocolo de confirmação (sinalização ACK e NAK) que requer explicitamente a repetição de TLPs não reconhecidos/ruins,

- inicializar e gerenciar créditos de controle de fluxo

No lado da transmissão, a camada de enlace de dados gera um número de sequência crescente para cada TLP de saída. Ele serve como uma etiqueta de identificação única para cada TLP transmitido e é inserido no cabeçalho do TLP de saída. Um código de verificação de redundância cíclica de 32 bits (conhecido neste contexto como Link CRC ou LCRC) também é anexado ao final de cada TLP de saída.

No lado do recebimento, o LCRC e o número de sequência do TLP recebido são validados na camada de enlace. Se a verificação de LCRC falhar (indicando um erro de dados) ou o número de sequência estiver fora do intervalo (não consecutivo do último TLP válido recebido), o TLP incorreto, bem como quaisquer TLPs recebidos após o TLP incorreto, são considerados inválidos e descartados. O receptor envia uma mensagem de confirmação negativa (NAK) com o número de sequência do TLP inválido, solicitando a retransmissão de todos os TLPs para frente desse número de sequência. Se o TLP recebido passar na verificação LCRC e tiver o número de sequência correto, ele será tratado como válido. O receptor de link incrementa o número de sequência (que rastreia o último TLP bom recebido) e encaminha o TLP válido para a camada de transação do receptor. Uma mensagem ACK é enviada ao transmissor remoto, indicando que o TLP foi recebido com sucesso (e, por extensão, todos os TLPs com números de sequência anteriores).

Se o transmissor receber uma mensagem NAK ou nenhuma confirmação (NAK ou ACK) for recebida até que um período de tempo limite expire, o transmissor deverá retransmitir todos os TLPs que não possuem uma confirmação positiva (ACK). Salvo um mau funcionamento persistente do dispositivo ou meio de transmissão, a camada de enlace apresenta uma conexão confiável com a camada de transação, uma vez que o protocolo de transmissão garante a entrega de TLPs em um meio não confiável.

Além de enviar e receber TLPs gerados pela camada de transação, a camada de enlace de dados também gera e consome pacotes de camada de enlace de dados (DLLPs). Os sinais ACK e NAK são comunicados via DLLPs, assim como algumas mensagens de gerenciamento de energia e informações de crédito de controle de fluxo (em nome da camada de transação).

Na prática, o número de TLPs não reconhecidos em voo no link é limitado por dois fatores: o tamanho do buffer de repetição do transmissor (que deve armazenar uma cópia de todos os TLPs transmitidos até que o receptor remoto os confirme) e o controle de fluxo créditos emitidos pelo receptor para um transmissor. O PCI Express exige que todos os receptores emitam um número mínimo de créditos, para garantir que um link permita o envio de TLPs PCIConfig e TLPs de mensagens.

Camada de transação

[editar | editar código-fonte]O PCI Express implementa transações divididas (transações com solicitação e resposta separadas por tempo), permitindo que o link transporte outro tráfego enquanto o dispositivo de destino coleta dados para a resposta.

PCI Express usa controle de fluxo baseado em crédito. Nesse esquema, um dispositivo anuncia um valor inicial de crédito para cada buffer recebido em sua camada de transação. O dispositivo na extremidade oposta do link, ao enviar transações para este dispositivo, conta o número de créditos que cada TLP consome de sua conta. O dispositivo emissor só pode transmitir um TLP quando isso não fizer com que sua contagem de crédito consumido exceda seu limite de crédito. Quando o dispositivo receptor termina de processar o TLP de seu buffer, ele sinaliza um retorno de créditos ao dispositivo emissor, o que aumenta o limite de crédito pelo valor restaurado. Os contadores de crédito são contadores modulares, e a comparação dos créditos consumidos com o limite de crédito requer aritmética modular. A vantagem desse esquema (em comparação com outros métodos, como estados de espera ou protocolos de transferência baseados em handshake) é que a latência do retorno de crédito não afeta o desempenho, desde que o limite de crédito não seja encontrado. Essa suposição geralmente é atendida se cada dispositivo for projetado com tamanhos de buffer adequados.

PCIe 1.x é frequentemente citado para suportar uma taxa de dados de 250 MB/s em cada direção, por pista. Esta figura é um cálculo da taxa de sinalização física (2,5 gigabaud) dividida pela sobrecarga de codificação (10 bits por byte). Isso significa que uma placa PCIe de dezesseis pistas (x16) seria teoricamente capaz de 16x250 MB/s = 4 GB/s em cada direção. Embora isso seja correto em termos de bytes de dados, cálculos mais significativos são baseados na taxa de carga útil de dados utilizável, que depende do perfil do tráfego, que é uma função do aplicativo de alto nível (software) e dos níveis de protocolo intermediários.

Como outros sistemas de interconexão serial de alta taxa de dados, o PCIe possui um protocolo e sobrecarga de processamento devido à robustez de transferência adicional (CRC e confirmações). Transferências unidirecionais longas e contínuas (como as típicas em controladores de armazenamento de alto desempenho) podem se aproximar de >95% da taxa de dados brutos (pista) do PCIe. Essas transferências também se beneficiam mais com o aumento do número de vias (x2, x4, etc.). Mas em aplicações mais típicas (como um controlador USB ou Ethernet), o perfil de tráfego é caracterizado como pacotes de dados curtos com reconhecimentos obrigatórios frequentes.[carece de fontes] Esse tipo de tráfego reduz a eficiência do link, devido à sobrecarga da análise de pacotes e interrupções forçadas (na interface do host do dispositivo ou na CPU do PC). Sendo um protocolo para dispositivos conectados à mesma placa de circuito impresso, não requer a mesma tolerância a erros de transmissão que um protocolo para comunicação a distâncias maiores e, portanto, essa perda de eficiência não é específica do PCIe.

Eficiência do link

[editar | editar código-fonte]Quanto a qualquer link de comunicação "tipo rede", parte da largura de banda "bruta" é consumida pela sobrecarga do protocolo:[113]

Uma via PCIe 1.x, por exemplo, oferece uma taxa de dados sobre a camada física de 250 MB/s (simplex). Esta não é a largura de banda de carga útil, mas a largura de banda da camada física – uma pista PCIe precisa transportar informações adicionais para funcionalidade total.[113]

| Camada | PHY | Camada de enlace de dados | Transação | Camada de enlace de dados | PHY | ||

|---|---|---|---|---|---|---|---|

| Dados | Start | Seqüência | Cabeçalho | Carga útil | ECRC | LCRC | Fim |

| Tamanho (Bytes) | 1 | 2 | 12 ou 16 | 0 a 4096 | 4 (opcional) | 4 | 1 |

A sobrecarga Gen2 é então de 20, 24 ou 28 bytes por transação.[carece de fontes]

| Camada | G3 PHY | Camada de enlace de dados | Camada de Transação | Camada de enlace de dados | ||

|---|---|---|---|---|---|---|

| Dados | Start | Seqüência | Cabeçalho | Carga útil | ECRC | LCRC |

| Tamanho (Bytes) | 4 | 2 | 12 ou 16 | 0 a 4096 | 4 (opcional) | 4 |

A sobrecarga Gen3 é então de 22, 26 ou 30 bytes por transação.[carece de fontes]

O para uma carga útil de 128 bytes é 86% e 98% para uma carga útil de 1024 bytes. Para pequenos acessos como configurações de registro (4 bytes), a eficiência cai para até 16%.[carece de fontes]

O tamanho máximo da carga útil (MPS) é definido em todos os dispositivos com base no menor máximo em qualquer dispositivo na cadeia. Se um dispositivo possui um MPS de 128 bytes, todos os dispositivos da árvore devem definir seus MPS para 128 bytes. Nesse caso, o barramento terá uma eficiência de pico de 86% para gravações.[113]:3

Aplicações

[editar | editar código-fonte]

O PCI Express opera em aplicativos de consumo, servidor e industriais, como uma interconexão no nível da placa-mãe (para conectar periféricos montados na placa-mãe), uma interconexão de backplane passiva e uma interface de placa de expansão para placas adicionais.

Em praticamente todos os PCs modernos (a partir de 2012), de laptops e desktops de consumo a servidores de dados corporativos, o barramento PCIe serve como a principal interconexão no nível da placa-mãe, conectando o processador do sistema host com periféricos integrados (ICs montados em superfície) e periféricos adicionais (placas de expansão). Na maioria desses sistemas, o barramento PCIe coexiste com um ou mais barramentos PCI legados, para compatibilidade retroativa com o grande corpo de periféricos PCI legados.

A partir de 2013, o PCI Express substituiu o AGP como interface padrão para placas gráficas em novos sistemas. Quase todos os modelos de placas gráficas lançados desde 2010 pela AMD (ATI) e Nvidia usam PCI Express. A Nvidia usa a transferência de dados de alta largura de banda do PCIe para sua tecnologia Scalable Link Interface (SLI), que permite que várias placas gráficas do mesmo chipset e número de modelo sejam executadas em conjunto, permitindo maior desempenho.[carece de fontes] A AMD também desenvolveu um sistema multi-GPU baseado em PCIe chamado CrossFire.[carece de fontes] AMD, Nvidia e Intel lançaram chipsets de placas-mãe que suportam até quatro slots PCIe x16, permitindo configurações de placa tri-GPU e quad-GPU.

GPUs externas

[editar | editar código-fonte]Teoricamente, o PCIe externo poderia dar a um notebook o poder gráfico de um desktop, conectando um notebook a qualquer placa de vídeo PCIe de desktop (incluída em sua própria caixa externa, com fonte de alimentação e refrigeração); isso é possível com uma interface ExpressCard ou Thunderbolt. Uma interface ExpressCard fornece taxas de bits de 5 Gbit/s (taxa de transferência de 0,5 GB/s), enquanto uma interface Thunderbolt fornece taxas de bits de até 40 Gbit/s (taxa de transferência de 5 GB/s).

Em 2006, a Nvidia desenvolveu a família de GPUs PCIe externo Quadro Plex que pode ser usado para aplicativos gráficos avançados para o mercado profissional.[114] Essas placas de vídeo requerem um slot PCI Express x8 ou x16 para a placa do lado do host, que se conecta ao Plex por meio de um VHDCI transportando oito pistas PCIe.[115]

Em 2008, a AMD anunciou a tecnologia ATI XGP, baseada em um sistema de cabeamento proprietário que é compatível com transmissões de sinal PCIe x8.[116] Este conector está disponível nos notebooks Fujitsu Amilo e Acer Ferrari One. A Fujitsu lançou seu gabinete AMILO GraphicBooster para XGP logo em seguida.[117] Por volta de 2010, a Acer lançou o dock gráfico Dynavivid para XGP.[118]

Em 2010, foram introduzidos hubs de placas externas que podem se conectar a um laptop ou desktop por meio de um slot PCI ExpressCard. Esses hubs podem aceitar placas gráficas de tamanho normal. Exemplos incluem MSI GUS,[119] ViDock da Village Instrument,[120] Asus XG Station, adaptador Bplus PE4H V3.2,[121] bem como dispositivos DIY mais improvisados.[122] No entanto, essas soluções são limitadas pelo tamanho (geralmente apenas x1) e pela versão do slot PCIe disponível em um laptop.

A interface Intel Thunderbolt forneceu uma nova opção para conectar-se a uma placa PCIe externamente. A Magma lançou o ExpressBox 3T, que pode conter até três placas PCIe (duas em x8 e uma em x4).[123] A MSI também lançou o Thunderbolt GUS II, um chassi PCIe dedicado para placas de vídeo.[124] Outros produtos como o Echo Express da Sonnet[125] e o mLink da mLogic são chassis Thunderbolt PCIe em um formato menor.[126]

Em 2017, foram introduzidos hubs de placas externas com mais recursos, como o Razer Core, que possui uma interface PCIe x16 completa.[127]

Dispositivos de armazenamento

[editar | editar código-fonte]

O protocolo PCI Express pode ser usado como interface de dados para dispositivos de memória flash, como cartões de memória e unidades de estado sólido (SSDs).

O cartão XQD é um formato de cartão de memória que utiliza PCI Express, desenvolvido pela CompactFlash Association, com taxas de transferência de até 1 GB/s.[128]

Muitos SSDs de classe empresarial de alto desempenho são projetados como placas controladoras PCI Express RAID.[carece de fontes] Antes do NVMe ser padronizado, muitas dessas placas utilizavam interfaces proprietárias e drivers personalizados para se comunicar com o sistema operacional; eles tinham taxas de transferência muito mais altas (mais de 1 GB/s) e IOPS (mais de um milhão de operações de E/S por segundo) quando comparados aos drives Serial ATA ou SAS.[quanto?][129][130] Por exemplo, em 2011, a OCZ e a Marvell co-desenvolveram um controlador de unidade de estado sólido PCI Express nativo para um slot PCI Express 3.0 x16 com capacidade máxima de 12 TB e desempenho de transferências sequenciais de até 7,2 GB/s e até 2,52 milhões de IOPS em transferências aleatórias.[131]

SATA Express era uma interface para conectar SSDs através de portas compatíveis com SATA, opcionalmente fornecendo várias pistas PCI Express como uma conexão PCI Express pura para o dispositivo de armazenamento conectado.[132] M.2 é uma especificação para placas de expansão de computador montadas internamente e conectores associados, que também usa várias pistas PCI Express.[133]

Os dispositivos de armazenamento PCI Express podem implementar a interface lógica AHCI para compatibilidade com versões anteriores e a interface lógica NVM Express para operações de E/S muito mais rápidas, fornecidas pela utilização do paralelismo interno oferecido por esses dispositivos. SSDs de classe empresarial também podem implementar SCSI sobre PCI Express.[134]

Interconexão de cluster

[editar | editar código-fonte]Certos aplicativos de data center (como grandes clusters de computador) exigem o uso de interconexões de fibra óptica devido às limitações de distância inerentes ao cabeamento de cobre. Normalmente, um padrão orientado à rede, como Ethernet ou Fibre Channel, é suficiente para esses aplicativos, mas em alguns casos a sobrecarga introduzida por protocolos roteáveis é indesejável e é necessária uma interconexão de nível inferior, como InfiniBand, RapidIO ou NUMAlink. Padrões de barramento local como PCIe e HyperTransport podem, em princípio, ser usados para esse fim,[135] mas a partir de 2015, as soluções estão disponíveis apenas em fornecedores de nicho, como Dolphin ICS e TTTech Auto.

Procolos concorrentes

[editar | editar código-fonte]Outros padrões de comunicação baseados em arquiteturas seriais de alta largura de banda incluem InfiniBand, RapidIO, HyperTransport, Intel QuickPath Interconnect e Mobile Industry Processor Interface (MIPI). As diferenças são baseadas nas compensações entre flexibilidade e extensibilidade versus latência e sobrecarga. Por exemplo, tornar o sistema hot-pluggable, como no Infiniband, mas não no PCI Express, requer que o software rastreie alterações na topologia da rede.[carece de fontes]

Outro exemplo é tornar os pacotes mais curtos para diminuir a latência (como é necessário se um barramento deve operar como uma interface de memória). Pacotes menores significam que os cabeçalhos dos pacotes consomem uma porcentagem maior do pacote, diminuindo assim a largura de banda efetiva. Exemplos de protocolos de barramento projetados para essa finalidade são RapidIO e HyperTransport.[carece de fontes]

O PCI Express fica em algum lugar no meio, direcionado por design como uma interconexão de sistema (barramento local) em vez de uma interconexão de dispositivos ou protocolo de rede roteado. Além disso, seu objetivo de design de transparência de software restringe o protocolo e aumenta um pouco sua latência.[carece de fontes]

Atrasos nas implementações do PCIe 4.0 levaram ao consórcio Gen-Z, ao esforço CCIX e a uma Coherent Accelerator Processor Interface (CAPI) aberta, todos anunciados até o final de 2016.[136]

Em 11 de março de 2019, a Intel apresentou o Compute Express Link (CXL), um novo barramento de interconexão, baseado na infraestrutura de camada física PCI Express 5.0. Os promotores iniciais da especificação CXL incluíam: Alibaba, Cisco, Dell EMC, Facebook, Google, HPE, Huawei, Intel e Microsoft.[137]

Lista de integradores

[editar | editar código-fonte]A Lista de Integradores PCI-SIG lista produtos feitos por empresas membros do PCI-SIG que passaram nos testes de conformidade. A lista inclui switches, bridges, NICs, SSDs, etc.[138]

Ver também

[editar | editar código-fonte]Notas

- ↑ Os switches podem criar vários endpoints de um para permitir o compartilhamento com vários dispositivos.

- ↑ O conector de alimentação Serial ATA da placa está presente porque as portas USB 3.0 requerem mais energia do que o barramento PCI Express pode fornecer. Mais frequentemente, um conector de alimentação Molex de 4 pinos é usado.

Referências

- ↑ Mayhew, D.; Krishnan, V. (Agosto de 2003). «PCI express and advanced switching: Evolutionary path to building next generation interconnects». 11th Symposium on High Performance Interconnects, 2003. Proceedings. [S.l.: s.n.] pp. 21–29. ISBN 0-7695-2012-X. doi:10.1109/CONECT.2003.1231473

- ↑ «Definition of PCI Express». PCMag. Cópia arquivada em 6 de março de 2016

- ↑ Zhang, Yanmin; Nguyen, T Long (Junho 2007). «Enable PCI Express Advanced Error Reporting in the Kernel» (PDF). Proceedings of the Linux Symposium. Fedora project. Consultado em 23 de outubro de 2022. Arquivado do original (PDF) em 10 de março de 2016

- ↑ https://www.hyperstone.com Flash Memory Form Factors – The Fundamentals of Reliable Flash Storage, Retrieved 19 April 2018

- ↑ a b c Ravi Budruk (21 de agosto de 2007). «PCI Express Basics». PCI-SIG. Consultado em 23 de outubro de 2022. Arquivado do original (PDF) em 15 de julho de 2014

- ↑ «What are PCIe Slots and Their Uses». PC Guide 101. 18 de maio de 2021. Consultado em 11 de outubro de 2022

- ↑ «How PCI Express Works». How Stuff Works. 17 de agosto de 2005. Consultado em 23 de outubro de 2022. Cópia arquivada em 3 de dezembro de 2009

- ↑ «4.2.4.9. Link Width and Lane Sequence Negotiation», PCI Express Base Specification, Revision 2.1., 4 de março de 2009

- ↑ a b c «PCI Express Architecture Frequently Asked Questions». PCI-SIG. Consultado em 23 de outubro de 2022. Arquivado do original em 13 de novembro de 2008

- ↑ «PCI Express Bus». Interface bus. Consultado em 23 de outubro de 2022. Arquivado do original em 8 de dezembro de 2007

- ↑ 32 lanes are defined by the PCIe Base Specification up to PCIe 5.0 but there's no card standard in the PCIe Card Electromechanical Specification and that lane number was never implemented.

- ↑ «PCI Express – An Overview of the PCI Express Standard». Developer Zone. National Instruments. 13 de agosto de 2009. Consultado em 23 de outubro de 2022. Arquivado do original em 5 de janeiro de 2010

- ↑ a b Qazi, Atif. «What are PCIe Slots?». PC Gear Lab. Consultado em 8 de abril de 2020

- ↑ «New PCIe Form Factor Enables Greater PCIe SSD Adoption». NVM Express. 12 de junho de 2012. Cópia arquivada em 6 de setembro de 2015

- ↑ «Memblaze PBlaze4 AIC NVMe SSD Review». StorageReview. 21 de dezembro de 2015

- ↑ Fulton, Kane (20 de julho de 2015). «19 graphics cards that shaped the future of gaming». TechRadar

- ↑ Leadbetter, Richard (16 de setembro de 2020). «Nvidia GeForce RTX 3080 review: welcome to the next level». Eurogamer

- ↑ «Sapphire Radeon RX 5700 XT Pulse Review | bit-tech.net». bit-tech.net (em inglês). Consultado em 23 de outubro de 2022

- ↑ «AMD Radeon™ RX 5700 XT 8GB GDDR6 THICC II – RX-57XT8DFD6». xfxforce.com. Consultado em 23 de outubro de 2022. Cópia arquivada em 27 de agosto de 2019

- ↑ «ROG Strix GeForce RTX 3080 OC Edition 10GB GDDR6X | Graphics Cards». rog.asus.com

- ↑ «What is the A side, B side configuration of PCI cards». Frequently Asked Questions. Adex Electronics. 1998. Consultado em 23 de outubro de 2022. Arquivado do original em 2 de novembro de 2011

- ↑ a b PCI Express Card Electromechanical Specification Revision 2.0

- ↑ «L1 PM Substates with CLKREQ, Revision 1.0a» (PDF). PCI-SIG. Consultado em 23 de outubro de 2022. Cópia arquivada (PDF) em 26 de outubro de 2017

- ↑ «Emergency Power Reduction Mechanism with PWRBRK Signal ECN» (PDF). PCI-SIG. Consultado em 23 de outubro de 2022. Cópia arquivada (PDF) em 9 de novembro de 2018

- ↑ PCI Express Card Electromechanical Specification Revision 1.1

- ↑ Schoenborn, Zale (2004), Board Design Guidelines for PCI Express Architecture (PDF), PCI-SIG, pp. 19–21, cópia arquivada (PDF) em 27 de março de 2016

- ↑ PCI Express Base Specification, Revision 1.1 Page 332

- ↑ «Where Does PCIe Cables Go – A Guide To Powering Graphics Cards?» (em inglês). 16 de janeiro de 2022. Consultado em 15 de outubro de 2022

- ↑ a b «Mini-Fit® PCI Express®* Wire to Board Connector System» (PDF). Consultado em 23 de outubro de 2022

- ↑ PCI Express x16 Graphics 150W-ATX Specification Revision 1.0

- ↑ PCI Express 225 W/300 W High Power Card Electromechanical Specification Revision 1.0

- ↑ PCI Express Card Electromechanical Specification Revision 3.0

- ↑ Yun Ling (16 de maio de 2008). «PCIe Electromechanical Updates». Consultado em 23 de outubro de 2022. Arquivado do original em 5 de novembro de 2015

- ↑ «MP1: Mini PCI Express / PCI Express Adapter». hwtools.net. 18 de julho de 2014. Consultado em 23 de outubro de 2022. Cópia arquivada em 3 de outubro de 2014

- ↑ «mSATA FAQ: A Basic Primer». Notebook review. Cópia arquivada em 12 de fevereiro de 2012

- ↑ «Eee PC Research». ivc (wiki). Consultado em 23 de outubro de 2022. Cópia arquivada em 30 de março de 2010

- ↑ «Desktop Board Solid-state drive (SSD) compatibility». Intel. Cópia arquivada em 2 de janeiro de 2016

- ↑ «How to distinguish the differences between M.2 cards | Dell US». www.dell.com. Consultado em 23 de outubro de 2022

- ↑ «PCI Express External Cabling 1.0 Specification». Consultado em 23 de outubro de 2022. Cópia arquivada em 10 de fevereiro de 2007

- ↑ «PCI Express External Cabling Specification Completed by PCI-SIG». PCI SIG. 7 de fevereiro de 2007. Consultado em 23 de outubro de 2022. Arquivado do original em 26 de novembro de 2013

- ↑ a b c «OCuLink connectors and cables support new PCIe standard». www.connectortips.com. Arquivado do original em 13 de março de 2017

- ↑ Mokosiy, Vitaliy (9 de outubro de 2020). «Untangling terms: M.2, NVMe, USB-C, SAS, PCIe, U.2, OCuLink». Medium (em inglês). Consultado em 23 de outubro de 2022

- ↑ «Get ready for M-PCIe testing», PC board design, EDN

- ↑ a b «PCI SIG discusses M‐PCIe oculink & 4th gen PCIe», UK, The Register, 13 de setembro de 2013, cópia arquivada em 29 de junho de 2017

- ↑ «PCI Express 4.0 Frequently Asked Questions». pcisig.com. PCI-SIG. Consultado em 23 de outubro de 2022. Cópia arquivada em 18 de maio de 2014

- ↑ a b c «PCI Express 3.0 Frequently Asked Questions». pcisig.com. PCI-SIG. Consultado em 1 de maio de 2014. Cópia arquivada em 1 de fevereiro de 2014

- ↑ «What does GT/s mean, anyway?». TM World. Consultado em 23 de outubro de 2022. Cópia arquivada em 14 de agosto de 2012

- ↑ «Deliverable 12.2». SE: Eiscat. Consultado em 23 de outubro de 2022. Arquivado do original em 17 de agosto de 2010

- ↑ PCI SIG, cópia arquivada em 6 de julho de 2008

- ↑ «PCI Express Base 2.0 specification announced» (PDF) (Nota de imprensa). PCI-SIG. 15 de janeiro de 2007. Consultado em 23 de outubro de 2022. Arquivado do original (PDF) em 4 de março de 2007 — note that in this press release the term aggregate bandwidth refers to the sum of incoming and outgoing bandwidth; using this terminology the aggregate bandwidth of full duplex 100BASE-TX is 200 Mbit/s.

- ↑ Smith, Tony (11 de outubro de 2006). «PCI Express 2.0 final draft spec published». The Register. Consultado em 23 de outubro de 2022. Arquivado do original em 29 de janeiro de 2007

- ↑ Key, Gary; Fink, Wesley (21 de maio de 2007). «Intel P35: Intel's Mainstream Chipset Grows Up». AnandTech. Consultado em 23 de outubro de 2022. Cópia arquivada em 23 de maio de 2007

- ↑ Huynh, Anh (8 de fevereiro de 2007). «NVIDIA "MCP72" Details Unveiled». AnandTech. Consultado em 23 de outubro de 2022. Arquivado do original em 10 de fevereiro de 2007

- ↑ «Intel P35 Express Chipset Product Brief» (PDF). Intel. Consultado em 23 de outubro de 2022. Cópia arquivada (PDF) em 26 de setembro de 2007